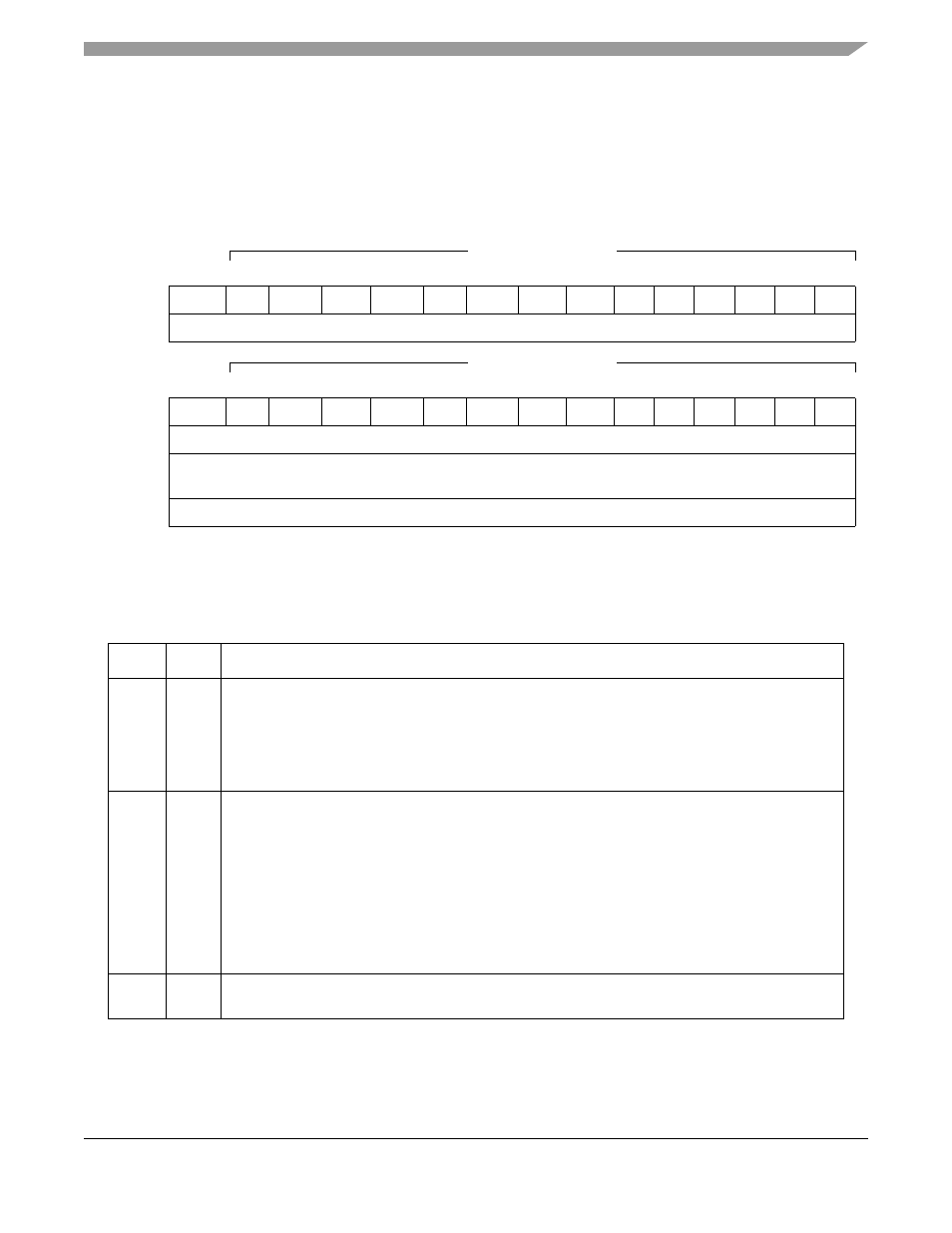

The tdr, shown in, Table 30-11 – Motorola ColdFire MCF5281 User Manual

Page 633

Debug Support

Freescale Semiconductor

30-15

NOTE

The debug module has no hardware interlocks, so to prevent spurious

breakpoint triggers while the breakpoint registers are being loaded, disable

TDR (by clearing TDR[29,13]) before defining triggers.

A write to TDR clears the CSR trigger status bits, CSR[BSTAT].

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Field

TRC

EBL

EDLW EDWL EDWU EDLL EDLM EDUM EDUU

DI

EAI

EAR EAL EPC

PCI

Reset

0000_0000_0000_0000

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Field

LxT

EBL

EDLW EDWL EDWU EDLL EDLM EDUM EDUU

DI

EAI

EAR EAL EPC

PCI

Reset

0000_0000_0000_0000

R/W Write only. Accessible in supervisor mode as debug control register 0x07 using the WDEBUG instruction and

through the BDM port using the

WDMREG

command.

DRc[4–0]

0x07

Figure 30-11. Trigger Definition Register (TDR)

Table 30-14. TDR Field Descriptions

Bits

Name

Description

31–30

TRC

Trigger response control. Determines how the processor responds to a completed trigger condition.

The trigger response is always displayed on DDATA.

00 Display on DDATA only

01 Processor halt

10 Debug interrupt

11 Reserved

15–14

LxT

Level-x trigger. This is a Rev. B function only. The Level-x Trigger bit determines the logic operation

for the trigger between the PC_condition and the (Address_range & Data_condition) where the

inclusion of a Data condition is optional. The ColdFire debug architecture supports the creation of

single or double-level triggers.

TDR[15]

0 Level-2 trigger = PC_condition & Address_range & Data_condition

1 Level-2 trigger = PC_condition | (Address_range & Data_condition)

TDR[14]

0 Level-1 trigger = PC_condition & Address_range & Data_condition

1 Level-1 trigger = PC_condition | (Address_range & Data_condition)

29/13

EBL

Enable breakpoint. Global enable for the breakpoint trigger. Setting TDR[EBL] enables a breakpoint

trigger. Clearing it disables all breakpoints at that level.

Second-Level Trigger

First-Level Trigger

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3