8 mii speed control register (mscr), 8 mii speed control register (mscr) -15 – Motorola ColdFire MCF5281 User Manual

Page 325

Fast Ethernet Controller (FEC)

Freescale Semiconductor

17-15

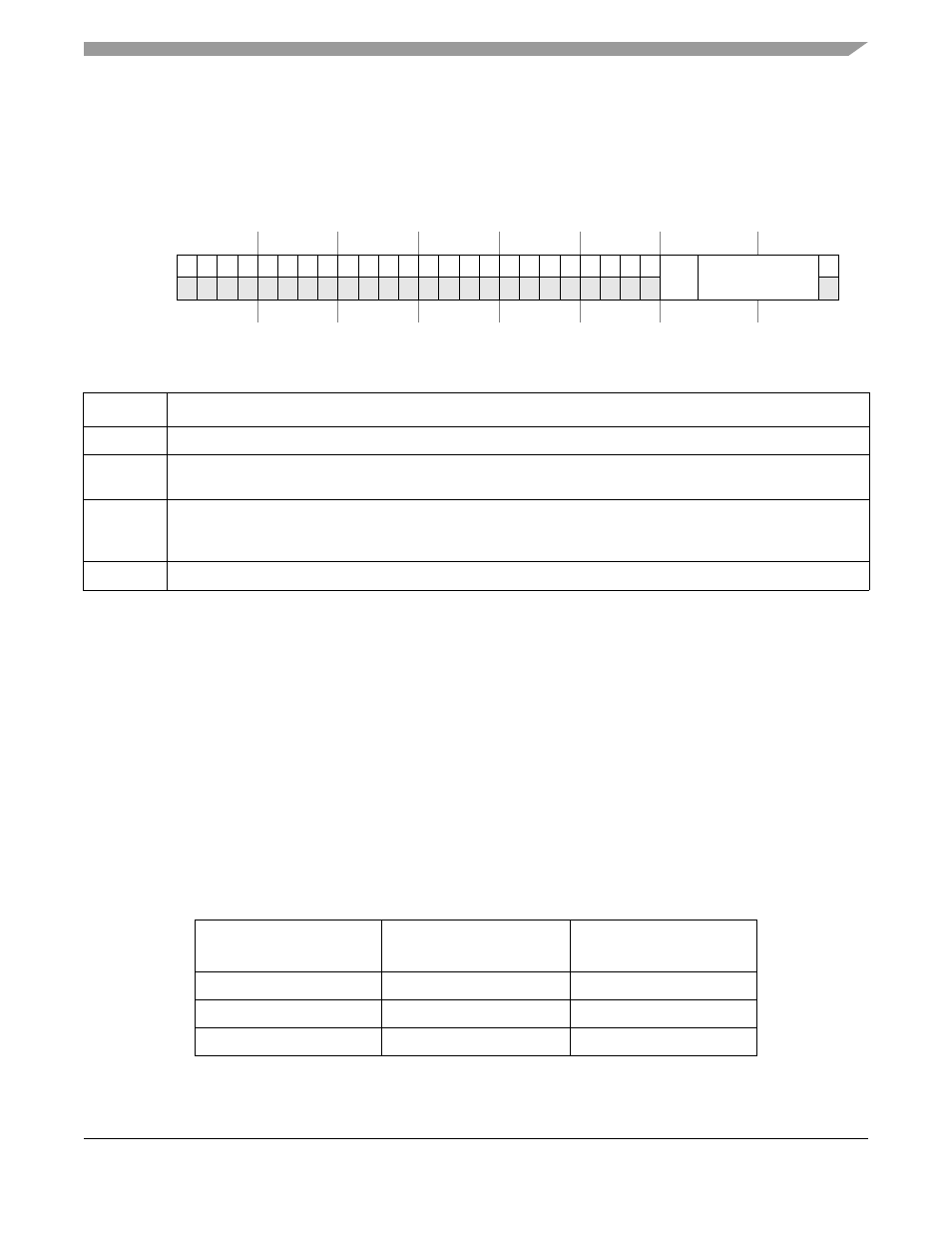

17.4.8

MII Speed Control Register (MSCR)

The MSCR provides control of the MII clock (FEC_MDC pin) frequency and allows a preamble drop on

the MII management frame.

The MII_SPEED field must be programmed with a value to provide an FEC_MDC frequency of less than

or equal to 2.5 MHz to be compliant with the IEEE 802.3 MII specification. The MII_SPEED must be set

to a non-zero value to source a read or write management frame. After the management frame is complete,

the MSCR register may optionally be set to 0 to turn off the FEC_MDC. The FEC_MDC generated has a

50% duty cycle except when MII_SPEED changes during operation (change takes effect following a rising

or falling edge of FEC_MDC).

If the internal bus clock is 25 MHz, programming this register to 0x0000_0005 results in an FEC_MDC

as stated the equation below.

Eqn. 17-1

A table showing optimum values for MII_SPEED as a function of internal bus clock frequency is provided

below.

IPSBAR

Offset:

0x1044

Access: User read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 DIS_

PRE

MII_SPEED

0

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

0 0 0 0 0 0 0

Figure 17-8. MII Speed Control Register (MSCR)

Table 17-11. MSCR Field Descriptions

Field

Description

31–8

Reserved, must be cleared.

7

DIS_PRE

Setting this bit causes the preamble (32 ones) not to be prepended to the MII management frame. The MII

standard allows the preamble to be dropped if the attached PHY device(s) does not require it.

6–1

MII_SPEED

Controls the frequency of the MII management interface clock (FEC_MDC) relative to the internal bus clock. A

value of 0 in this field turns off the FEC_MDC and leaves it in low voltage state. Any non-zero value results in the

FEC_MDC frequency of 1/(MII_SPEED

×

2) of the internal bus frequency.

0

Reserved, must be cleared.

Table 17-12. Programming Examples for MSCR

Internal FEC Clock

Frequency

MSCR[MII_SPEED]

FEC_MDC frequency

25 MHz

0x5

2.50 MHz

33 MHz

0x7

2.36 MHz

40 MHz

0x8

2.50 MHz

25 MHz

1

5

2

Ч

------------

Ч

2.5 MHz

=

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3