4 prescaler divide register (presdiv), 5 flexcan control register 2 (canctrl2), Table 25-12 describes the presdiv fields – Motorola ColdFire MCF5281 User Manual

Page 492

FlexCAN

25-22

Freescale Semiconductor

25.5.4

Prescaler Divide Register (PRESDIV)

25.5.5

FlexCAN Control Register 2 (CANCTRL2)

describes the CANCTRL2 fields.

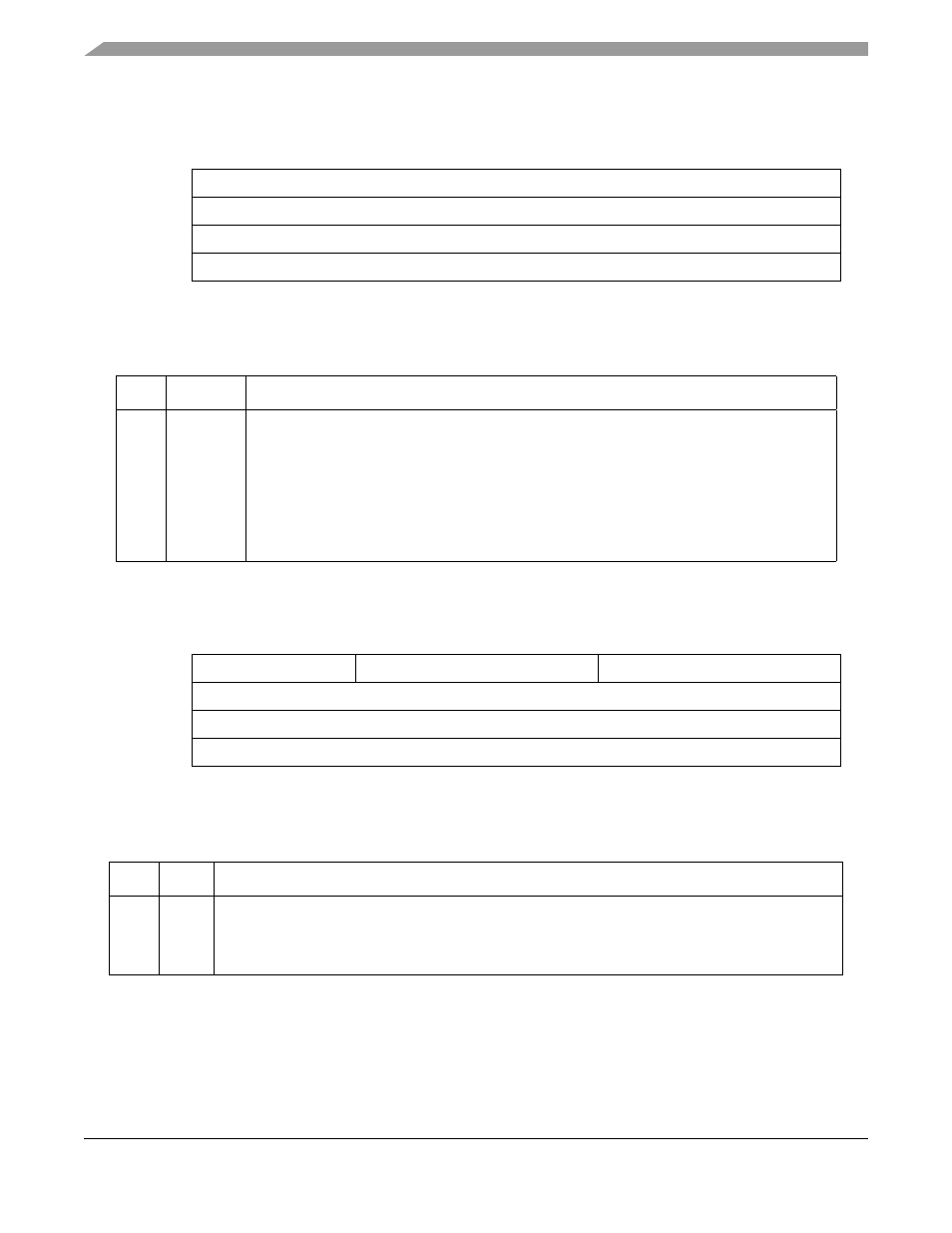

7

0

Field

PRES_DIV

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1C_0008

Figure 25-9. Prescaler Divide Register (PRESDIV)

Table 25-12. PRESDIV Field Descriptions

Bits

Name

Description

7–0

PRES_DIV Prescaler divide factor. PRESDIV determines the ratio between the system clock frequency and

the serial clock (S-clock). The S-clock is determined by the following calculation:

The reset value of PRESDIV is 0x00, which forces the S-clock to default to the same frequency

as the system clock. The valid programmed values are 0 through 255. See

” for more information.

7

6

5

3

2

0

Field

RJW

PSEG1

PSEG2

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1C_0009

Figure 25-10. FlexCAN Control Register 2 (CANCTRL2)

Table 25-13. CANCTRL2 Field Descriptions

Bits

Name

Description

7–6

RJW

Resynchronization jump width. The RJW field defines the maximum number of time quanta a bit time

may be changed during resynchronization. The valid programmed values are 0 through 3.

The resynchronization jump width is calculated as follows:

Resynchronizaton Jump Width = (RJW + 1) Time Quanta

S-clock

f

sys

2 PRESDIV + 1

(

)

---------------------------------------------

=

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3