3 grouped peripheral access control registers, Gpacr0 & gpacr1) -15 – Motorola ColdFire MCF5281 User Manual

Page 167

System Control Module (SCM)

Freescale Semiconductor

8-15

At reset, these on-chip modules are configured to have only supervisor read/write access capabilities. If an

instruction fetch access to any of these peripheral modules is attempted, the IPS bus cycle is immediately

terminated with an error.

8.6.3.3

Grouped Peripheral Access Control Registers (GPACR0 & GPACR1)

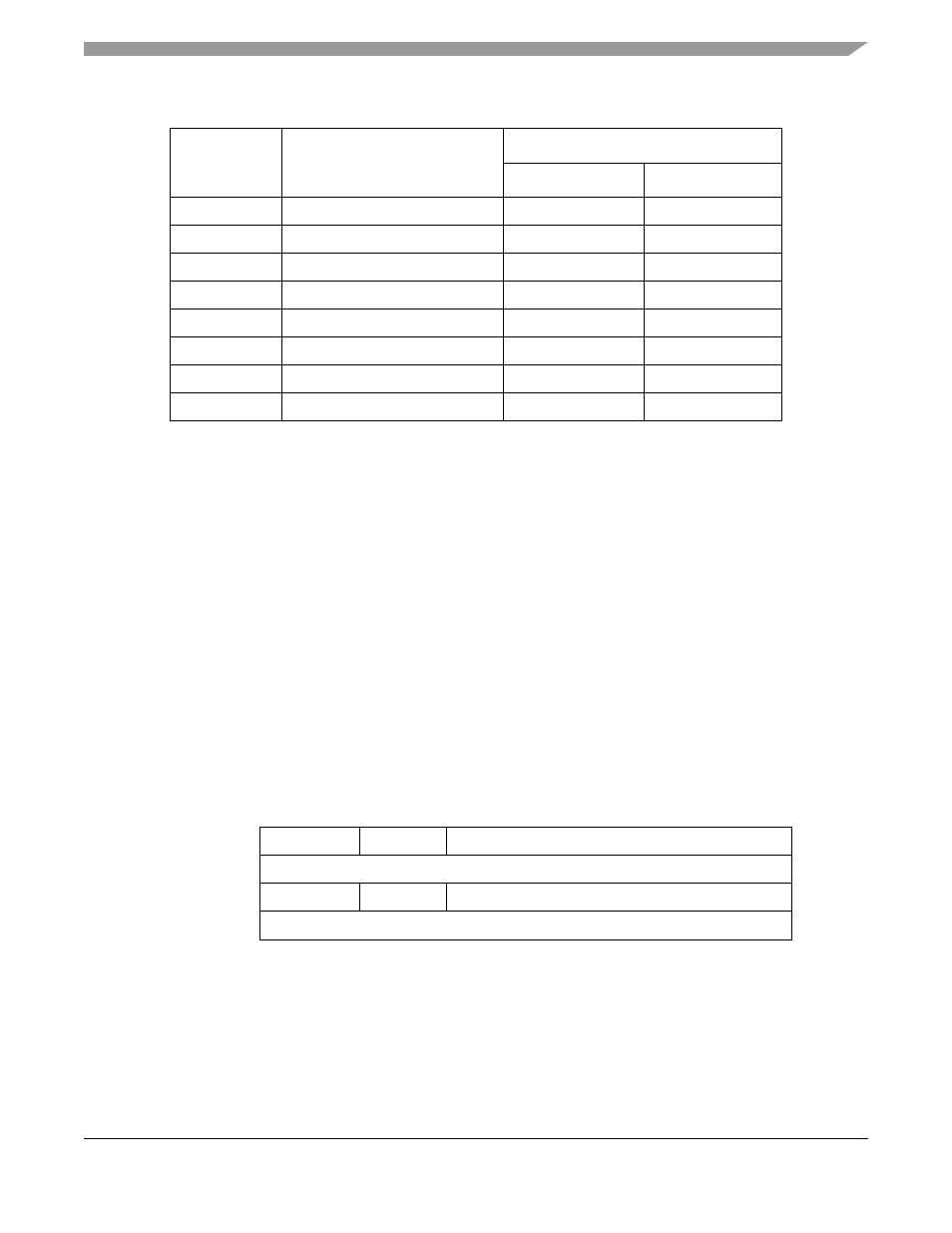

The on-chip peripheral space starting at IPSBAR is subdivided into sixteen 64-Mbyte regions. Each of the

first two regions has a unique access control register associated with it. The other fourteen regions are in

reserved space; the access control registers for these regions are not implemented. Bits [29:26] of the

address select the specific GPACRn to be used for a given reference within the IPS address space. These

access control registers are 8 bits in width so that read, write, and execute attributes may be assigned to the

given IPS region.

NOTE

The access control for modules with memory space protected by

PACR0–PACR8 are determined by the PACR0–PACR8 settings. The access

control is not affected by GPACR0, even though the modules are mapped in

its 64-Mbyte address space.

0x027

PACR3

UART2

—

0x028

PACR4

I

2

C

QSPI

0x029

—

—

—

0x02a

PACR5

DTIM0

DTIM1

0x02b

PACR6

DTIM2

DTIM3

0x02c

PACR7

INTC0

INTC1

0x02d

—

—

—

0x02e

PACR8

FEC0

—

7

6–4

3

0

Field

LOCK

—

ACCESS_CTRL

Reset

0000_0000

Read/Write

R/W

R

R/W

Address

IPSBAR + 0x030, IPSBAR + 0x31

Figure 8-10. Grouped Peripheral Access Control Register (GPACR)

Table 8-11. Peripheral Access Control Registers (PACRs) (continued)

IPSBAR Offset

Name

Modules Controlled

ACCESS_CTRL1

ACCESS_CTRL0

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3