3 functional description, 1 set-and-forget timer operation, 2 free-running timer operation – Motorola ColdFire MCF5281 User Manual

Page 366: 3 functional description -6, 1 set-and-forget timer operation -6, 2 free-running timer operation -6

Programmable Interrupt Timers (PIT0–PIT3)

19-6

Freescale Semiconductor

19.3

Functional Description

This section describes the PIT functional operation.

19.3.1

Set-and-Forget Timer Operation

This mode of operation is selected when the RLD bit in the PCSR register is set.

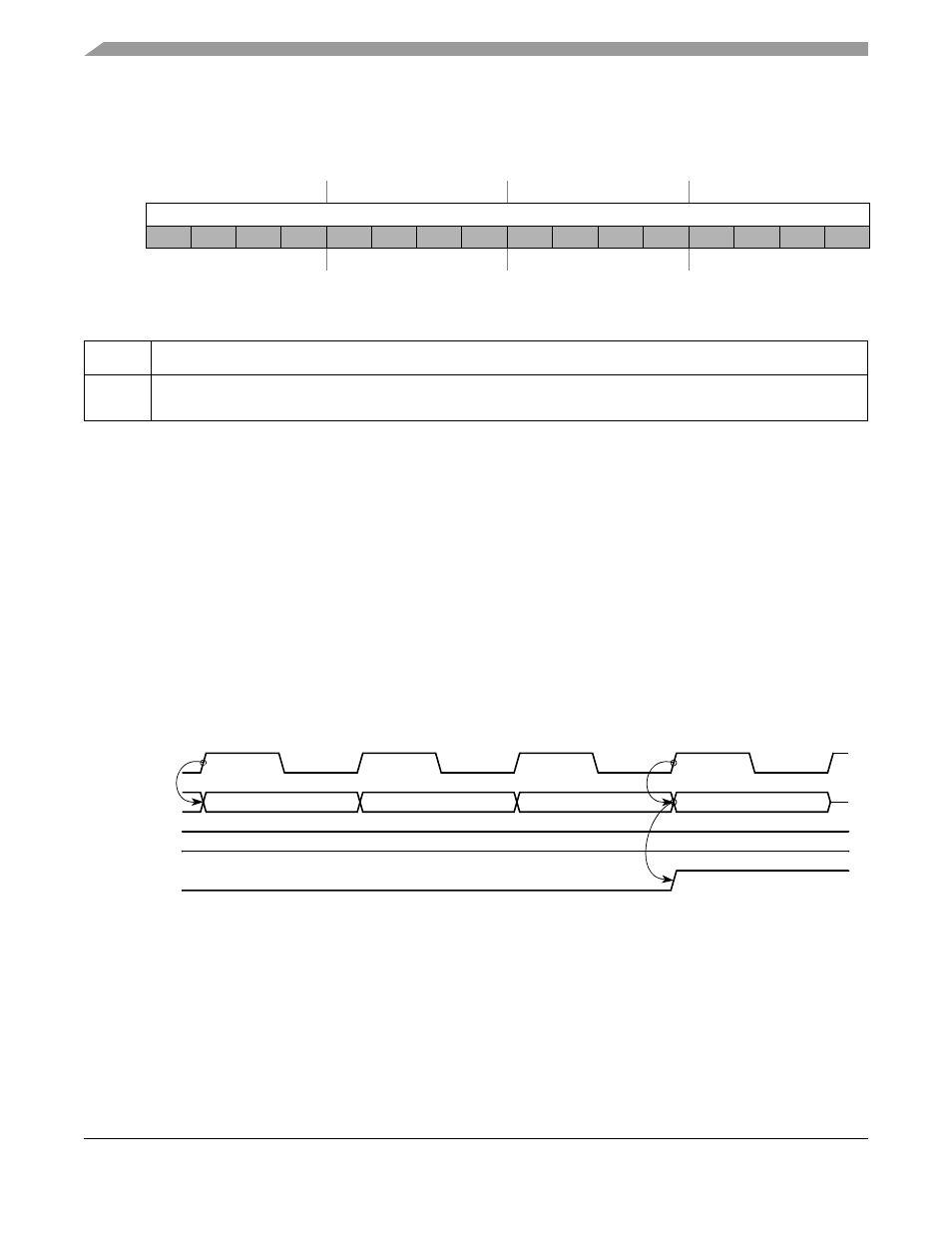

When PIT counter reaches a count of 0x0000, PIF flag is set in PCSRn. The value in the modulus register

loads into the counter, and the counter begins decrementing toward 0x0000. If the PCSRn[PIE] bit is set,

the PIF flag issues an interrupt request to the CPU.

When the PCSRn[OVW] bit is set, the counter can be directly initialized by writing to PMRn without

having to wait for the count to reach 0x0000.

Figure 19-5. Counter Reloading from the Modulus Latch

19.3.2

Free-Running Timer Operation

This mode of operation is selected when the PCSRn[RLD] bit is clear. In this mode, the counter rolls over

from 0x0000 to 0xFFFF without reloading from the modulus latch and continues to decrement.

When the counter reaches a count of 0x0000, PCSRn[PIF] flag is set. If the PCSRn[PIE] bit is set, PIF flag

issues an interrupt request to the CPU.

IPSBAR

Offset:

0x15_0004 (PCNTR0)

0x16_0004 (PCNTR

1

)

0x17_0004 (PCNTR

2

)

0x18_0004 (PCNTR

3

)

Access: User read only

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

PC

W

Reset

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Figure 19-4. PIT Count Register (PCNTRn)

Table 19-5. PCNTRn Field Descriptions

Field

Description

15–0

PC

Counter value. Reading this field with two 8-bit reads is not guaranteed coherent. Writing to PCNTRn has no effect,

and write cycles are terminated normally.

0x0002

0x0001

0x0000

0x0005

0x0005

PIT Clock

Counter

Modulus

PIF

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3