11 flexcan receive error counter (rxectr), 11flexcan receive error counter (rxectr) -29, Table 25-19 describes the iflag fields – Motorola ColdFire MCF5281 User Manual

Page 499: Table 25-20 describes the rxectr fields

FlexCAN

Freescale Semiconductor

25-29

25.5.11 FlexCAN Receive Error Counter (RXECTR)

15

14

13

12

11

10

9

8

Field

BUF15I

BUF14I

BUF13I

BUF1I

BUF11I

BUF10I

BUF9I

BUF8I

Reset

0000_0000

R/W

R/w

7

6

5

4

3

0

Field

BUF7I

BUF6I

BUF5I

BUF4I

BUF3I

BUF2I

BUF1I

BUF0I

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1C_0024

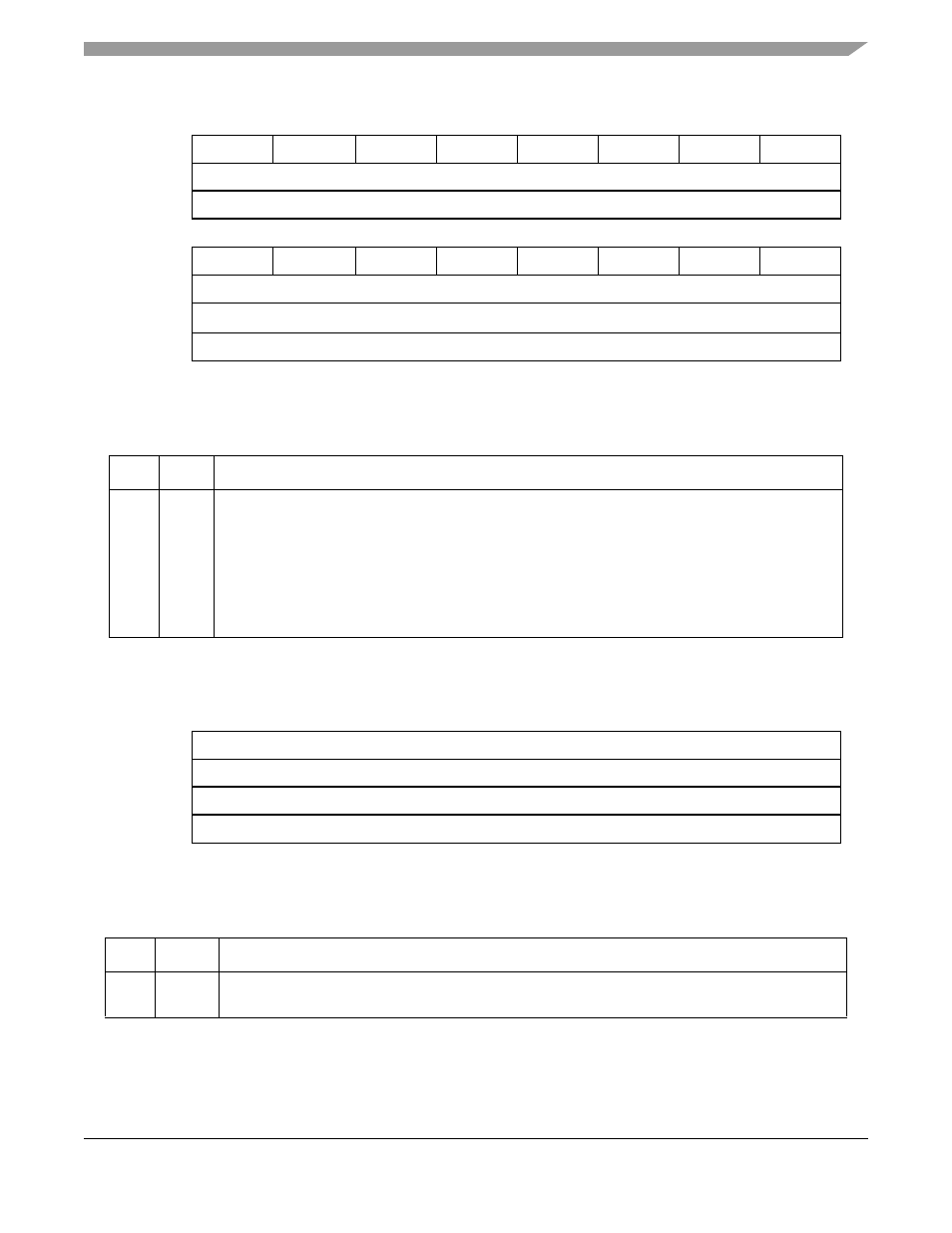

Figure 25-15. Interrupt Flag Register (IFLAG)

Table 25-19. IFLAG Field Descriptions

Bits

Name

Description

15–0

BUFnI IFLAG contains one interrupt flag bit per buffer. Each successful transmission/reception sets the

corresponding IFLAG bit and, if the corresponding IMASK bit is set, an interrupt request will be

generated.

To clear an interrupt flag, first read the flag as a one, and then write it as a one. Should a new flag

setting event occur between the time that the CPU reads the flag as a one and writes the flag as a

zero, the flag is not cleared. This register can be written to zeros only.

0 The interrupt for the corresponding buffer is disabled.

1 The interrupt for the corresponding buffer is enabled.

7

0

Field

RXECTR

Reset

0000_0000

R/W

R

Address

IPSBAR + 0x1C_0026

Figure 25-16. FlexCAN Receive Error Counter (RXECTR)

Table 25-20. RXECTR Field Descriptions

Bits

Name

Description

7–0

RXECT

R

Receive error counter. Indicates the current receive error count as defined in the CAN protocol. See

Section 25.4.9, “FlexCAN Error Counters

” for more details.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3