11 read debug module register (rdmreg), Command sequence – Motorola ColdFire MCF5281 User Manual

Page 653

Debug Support

Freescale Semiconductor

30-35

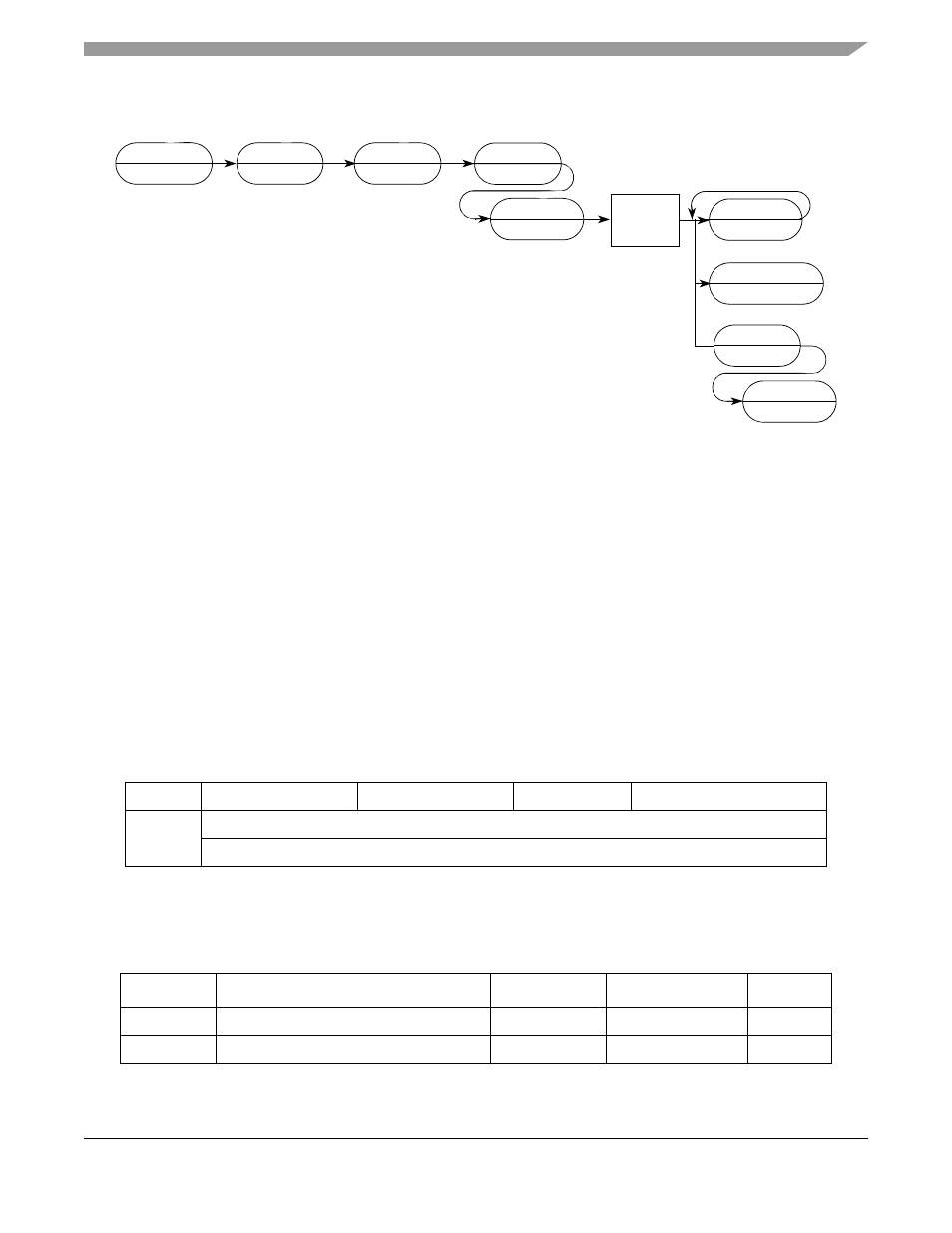

Command Sequence:

Figure 30-36.

WCREG

Command Sequence

Operand Data:

This instruction requires two longword operands. The first selects the register to

which the operand data is to be written; the second contains the data.

Result Data:

Successful write operations return 0xFFFF. Bus errors on the write cycle are

indicated by the setting of bit 16 in the status message and by a data pattern of

0x0001.

30.5.3.3.11 Read Debug Module Register (

RDMREG

)

Read the selected debug module register and return the 32-bit result. The only valid register selection for

the

RDMREG

command is CSR (DRc = 0x00). Note that this read of the CSR clears CSR[FOF, TRG, HALT,

BKPT]; as well as the trigger status bits (CSR[BSTAT]) if either a level-2 breakpoint has been triggered

or a level-1 breakpoint has been triggered and no level-2 breakpoint has been enabled.

Command/Result Formats:

shows the definition of DRc encoding.

15

12

11

8

7

5

4

0

Command

0x2

0xD

100

DRc

Result

D[31:16]

D[15:0]

Figure 30-37.

RDMREG

Command/Result Formats

Table 30-20. Definition of DRc Encoding—Read

DRc[4:0]

Debug Register Definition

Mnemonic

Initial State

Page

0x00

Configuration/Status

CSR

0x0

0x01–0x1F

Reserved

—

—

—

XXX

’NOT READY’

WCREG

???

MS ADDR

’NOT READY’

MS ADDR

’NOT READY’

WRITE

CONTROL

REGISTER

NEXT CMD

’CMD COMPLETE’

MS DATA

’NOT READY’

NEXT CMD

’NOT READY’

XXX

BERR

LS DATA

’NOT READY’

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3