2 sdram controller operation, 2 sdram controller operation -3 – Motorola ColdFire MCF5281 User Manual

Page 275

Synchronous DRAM Controller Module

Freescale Semiconductor

15-3

15.2

SDRAM Controller Operation

By running synchronously with the system clock, SDRAM can (after an initial latency period) be accessed

on every clock; 5-1-1-1 is a typical burst rate to the SDRAM. Unlike the MCF5272, this processor does

not have an independent SDRAM clock signal. For this processor, the timing of the SDRAM controller is

controlled by the CLKOUT signal.

Note that because the processor cannot have more than one page open at a time, it does not support

interleaving.

SDRAM controllers are more sophisticated than asynchronous DRAM controllers. Not only must they

manage addresses and data, but they must send special commands for such functions as precharge, read,

write, burst, auto-refresh, and various combinations of these functions.

lists common SDRAM

commands.

SDRAMs operate differently than asynchronous DRAMs, particularly in the use of data pipelines and

commands to initiate special actions. Commands are issued to memory using specific encodings on

address and control pins. Soon after system reset, a command must be sent to the SDRAM mode register

to configure SDRAM operating parameters.

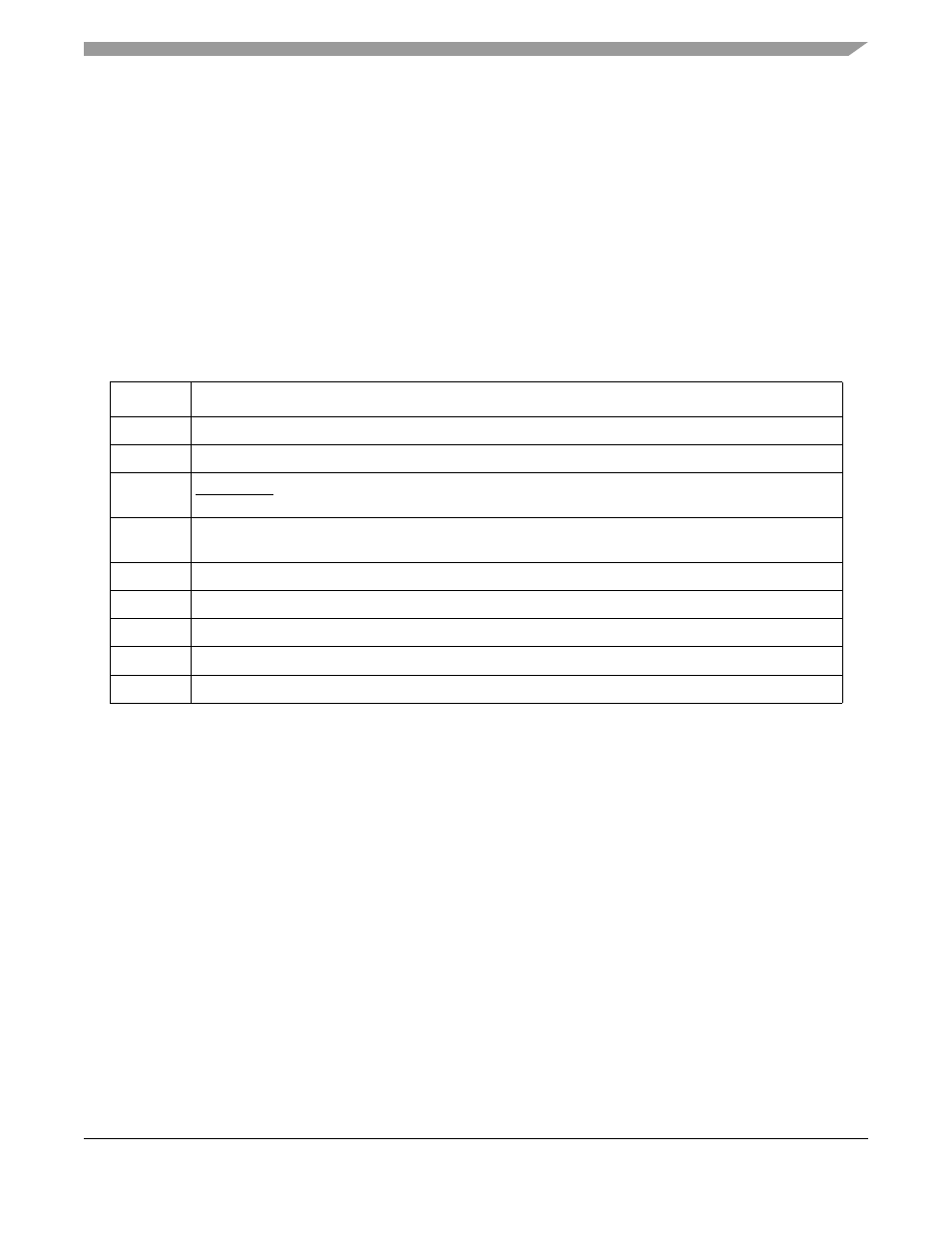

Table 15-1. SDRAM Commands

Command

Definition

ACTV

Activate. Executed before

READ

or

WRITE

executes; SDRAM registers and decodes row address.

MRS

Mode register set.

NOP

No-op. Does not affect SDRAM state machine; DRAM controller control signals negated;

SDRAM_CS[1:0] asserted.

PALL

Precharge all. Precharges all internal banks of an SDRAM component; executed before new page is

opened.

READ

Read access. SDRAM registers column address and decodes that a read access is occurring.

REF

Refresh. Refreshes internal bank rows of an SDRAM component.

SELF

Self refresh. Refreshes internal bank rows of an SDRAM component when it is in low-power mode.

SELFX

Exit self refresh. This command is sent to the DRAM controller when DCR[IS] is cleared.

WRITE

Write access. SDRAM registers column address and decodes that a write access is occurring.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3