Motorola ColdFire MCF5281 User Manual

Page 283

Synchronous DRAM Controller Module

Freescale Semiconductor

15-11

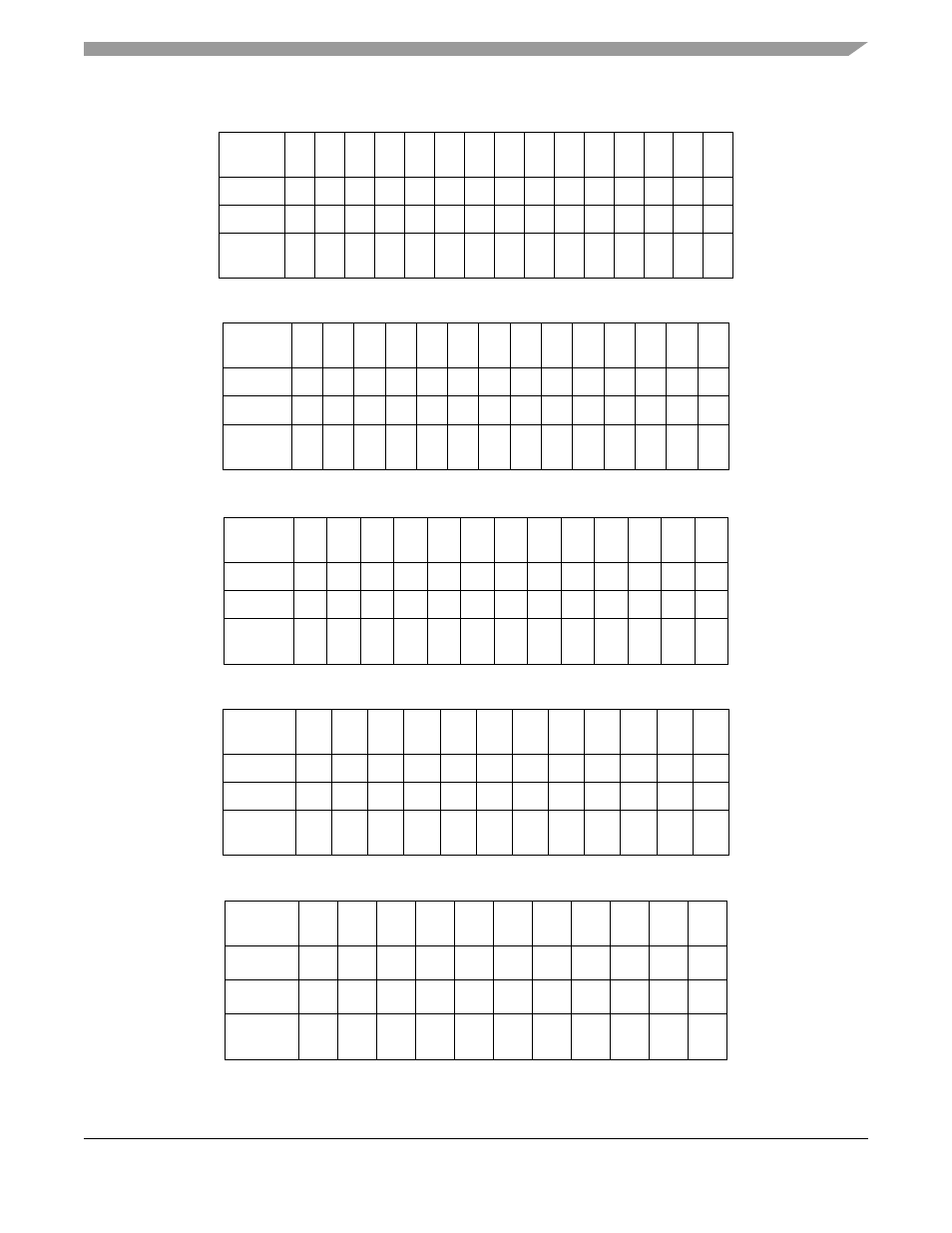

Table 15-13. Processor to SDRAM Interface (16-Bit Port, 8-Column Address Lines)

Process

or Pins

A16 A15 A14 A13 A12 A11 A10 A9 A17 A18 A19 A20 A21 A22 A23

Row

16

15

14

13

12

11

10

9

17

18

19

20

21

22

23

Column

1

2

3

4

5

6

7

8

SDRAM

Pins

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14

Table 15-14. Processor to SDRAM Interface (16-Bit Port, 9-Column Address Lines)

Processo

r Pins

A16 A15 A14 A13 A12 A11 A10 A9 A18 A19 A20 A21 A22 A23

Row

16

15

14

13

12

11

10

9

18

19

20

21

22

23

Column

1

2

3

4

5

6

7

8

17

SDRAM

Pins

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9 A10 A11 A12 A13

Table 15-15. Processor to SDRAM Interface (16-Bit Port, 10-Column Address Lines)

Processo

r Pins

A16 A15 A14 A13 A12 A11 A10 A9 A18 A20 A21 A22 A23

Row

16

15

14

13

12

11

10

9

18

20

21

22

23

Column

1

2

3

4

5

6

7

8

17

19

SDRAM

Pins

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9 A10 A11 A12

Table 15-16. Processor to SDRAM Interface (16-Bit Port, 11-Column Address Lines)

Processo

r Pins

A16 A15 A14 A13 A12 A11 A10

A9

A18 A20 A22 A23

Row

16

15

14

13

12

11

10

9

18

20

22

23

Column

1

2

3

4

5

6

7

8

17

19

21

SDRAM

Pins

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10 A11

Table 15-17. Processor to SDRAM Interface (16-Bit Port, 12-Column Address Lines)

Processor

Pins

A16

A15

A14

A13

A12

A11

A10

A9

A18

A20

A22

Row

16

15

14

13

12

11

10

9

18

20

22

Column

1

2

3

4

5

6

7

8

17

19

21

SDRAM

Pins

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3