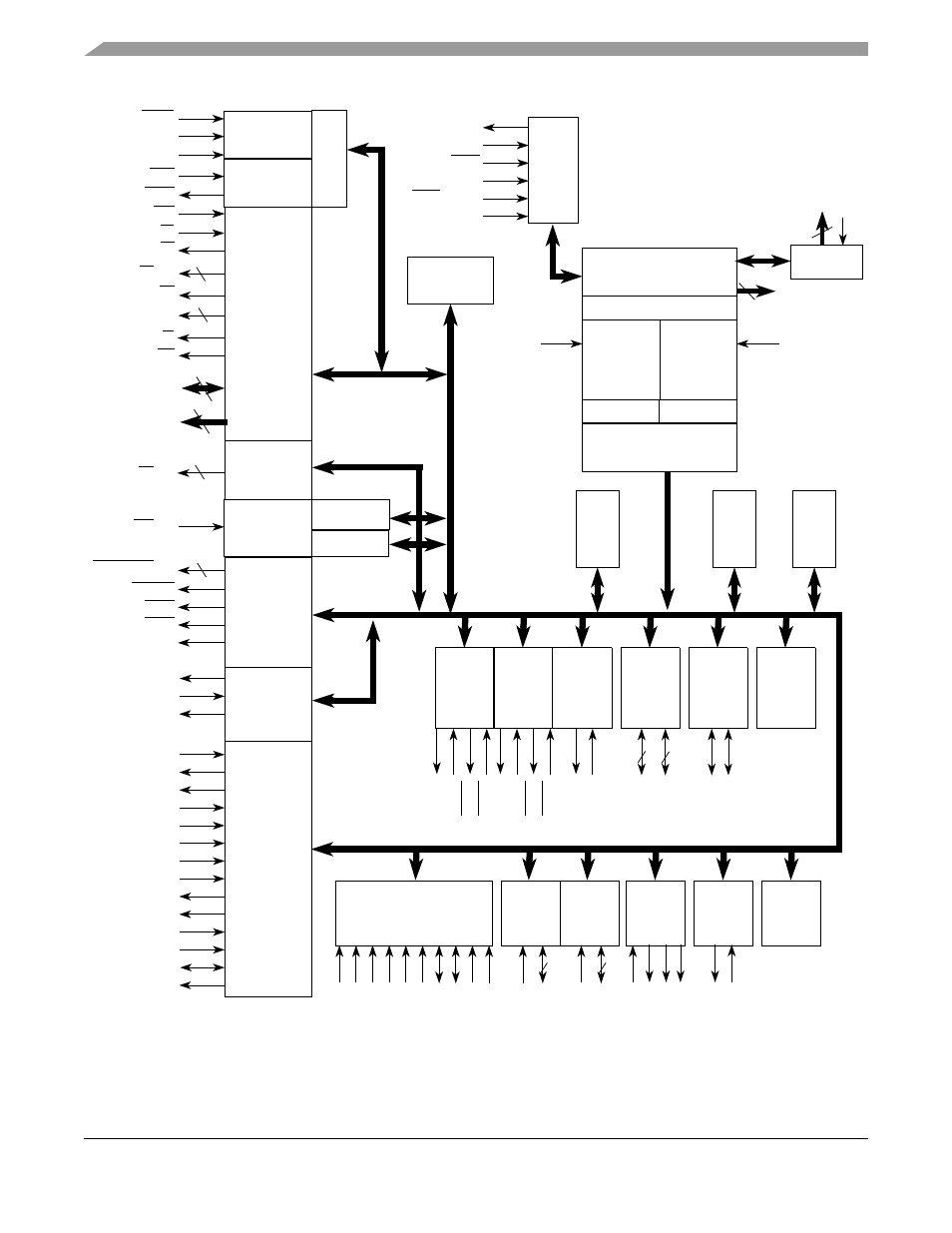

Figure 14-1, Shows the block diagram with the signal interface, 2 freescale semiconductor – Motorola ColdFire MCF5281 User Manual

Page 242

Signal Descriptions

14-2

Freescale Semiconductor

Figure 14-1. MCF5282 Block Diagram with Signal Interfaces

TDO/DSO

TDI/DSI

TMS/

BKPT

TCLK

Interface

Chip

UART1

Serial

I/O

EXTAL

DTIN

[3

:0

]

D

T

OUT[

3:

0]

TA

R/

W

SIZ[1:0]

D[31:0]

A[23:0]

JTAG

Port

Selects

External

UTxD0

URxD0

UR

T

S

0

UC

TS

0

UTxD1

URxD1

UR

T

S

1

UC

TS

1

DRAMW

2

24

32

BS

[3:0]

CS

[6:0]

7

4

2

TEA

TRST

/DSCLK

TEST

4

4

Test

Controller

OE

SRAS

SCAS

SCKE

TS

4

PS

T

[3:

0]

4

TIP

I

2

C

Module

SC

L

SD

A

UART2

Serial

I/O

DMA

Timer

Modules

DRAM

Controller

DDATA[3:0]

Clock Module

Chip

Configuration

Reset

Controller

Po

w

e

r

RCON

CLKMOD0

CLKMOD1

RSTI

RSTO

(PLL)

Edgeport

Interrupt

Controller 0

Interrupt

Controller 1

IRQ

[7:1]

FEC

UART0

Serial

I/O

DMA

Controlle

r

Watchdog

Timer

General

Purpose

Timer A

General

Purpose

Timer B

QSPI

FlexCAN

QADC

PIT

Timers

(PIT0–

JTAG_EN

CLKOUT

XTAL

ETXCLK

ETXEN

ETXDO

ECOL

ERXCLK

ERXDV

ERXD0

ECRS

ETXD[3:1]

ETXER

ERXD[3:1]

ERXER

EMDIO

EMDC

UTxD2

URxD2

(DTIM0–

DTIM3)

VREFH

VR

E

F

L

AN0/

ANW

AN

1

/AN

X

AN

2

/AN

Y

AN3/

ANZ

AN5

2/MA

0

AN5

3/MA

1

AN55/

TRIG

1

AN56/

TRIG

2

S

Y

NCA

GP

T

A

[3

:0

]

4

GP

T

B

[3

:0

]

4

S

Y

NCB

QSP

I_

D

IN

QS

PI

_DOUT

Q

S

PI

_C

LK

Q

S

PI

_

C

S[

3:

0

]

CANTX

CANRX

Mana

gemen

t

Module

Ports

Module

SDRAM_CS[1:0]

PIT3)

In

te

rn

a

l B

u

s

Arb

ite

r

Sy

st

em

Cont

rol

Module

(S

CM)

VDDF

VSTBY

Not present

and MCF5216

on MCF5214

Note:

ColdFire V2 Core

EMAC

2-Kbyte

D-Cache/I-Cache

Debug Module

DIV

Flash

Module

64K

SRAM

Note:

Not present

on MCF5280

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3