Motorola ColdFire MCF5281 User Manual

Page 252

Signal Descriptions

14-12

Freescale Semiconductor

External Memory Interface and Ports

C6:B6:A5

A[23:21]

PF[7:5]

CS[6:4]

Address bus

O

Yes

C4:B4:A4:B3:A3

A[20:16]

PF[4:0]

—

Address bus

O

Yes

A2:B1:B2:C1:

C2:C3:D1:D2

A[15:8]

PG[7:0]

—

Address bus

O

Yes

D3:D4:E1:E2:

E3:E4:F1:F2

A[7:0]

PH[7:0]

—

Address bus

O

Yes

F3:G1:G2:G3:

G4:H1:H2:H3

D[31:24]

PA[7:0]

—

Data bus

I/O

—

H4:J1:J2:J3:

J4:K1:K2:K3

D[23:16]

PB[7:0]

—

Data bus

I/O

—

L1:L2:L3:L4:

M1:M2:M3:M4

D[15:8]

PC[7:0]

—

Data bus

I/O

—

N1:N2:N3:P1:

N5:T6:R6:P6

D[7:0]

PD[7:0]

—

Data bus

I/O

—

P14:T15:R15:R16

BS[3:0]

PJ[7:4]

—

Byte strobe

I/O

Yes

N16

OE

PE7

—

Output enable

I/O

—

P16

TA

PE6

—

Transfer acknowledge

I/O

Yes

P15

TEA

PE5

—

Transfer error acknowledge

I/O

Yes

N15

R/W

PE4

—

Read/write

I/O

Yes

N14

SIZ1

PE3

SYNCA

Transfer size

I/O

Yes

3

M16

SIZ0

PE2

SYNCB

Transfer size

I/O

Yes

4

M15

TS

PE1

SYNCA

Transfer start

I/O

Yes

M14

TIP

PE0

SYNCB

Transfer in progress

I/O

Yes

Chip Selects

L16:L15:L14:L13

CS[3:0]

PJ[3:0]

—

Chip selects 3-0

I/O

Yes

C6:B6:A5

A[23:21]

PF[7:5]

CS[6:4]

Chip selects 6-4

O

Yes

SDRAM Controller

H15

SRAS

PSD5

—

SDRAM row address strobe

I/O

—

H16

SCAS

PSD4

—

SDRAM column address strobe

I/O

—

G15

DRAMW

PSD3

—

SDRAM write enable

I/O

—

H13:G16

SDRAM_CS[1:0]

PSD[2:1]

—

SDRAM chip selects

I/O

—

H14

SCKE

PSD0

—

SDRAM clock enable

I/O

—

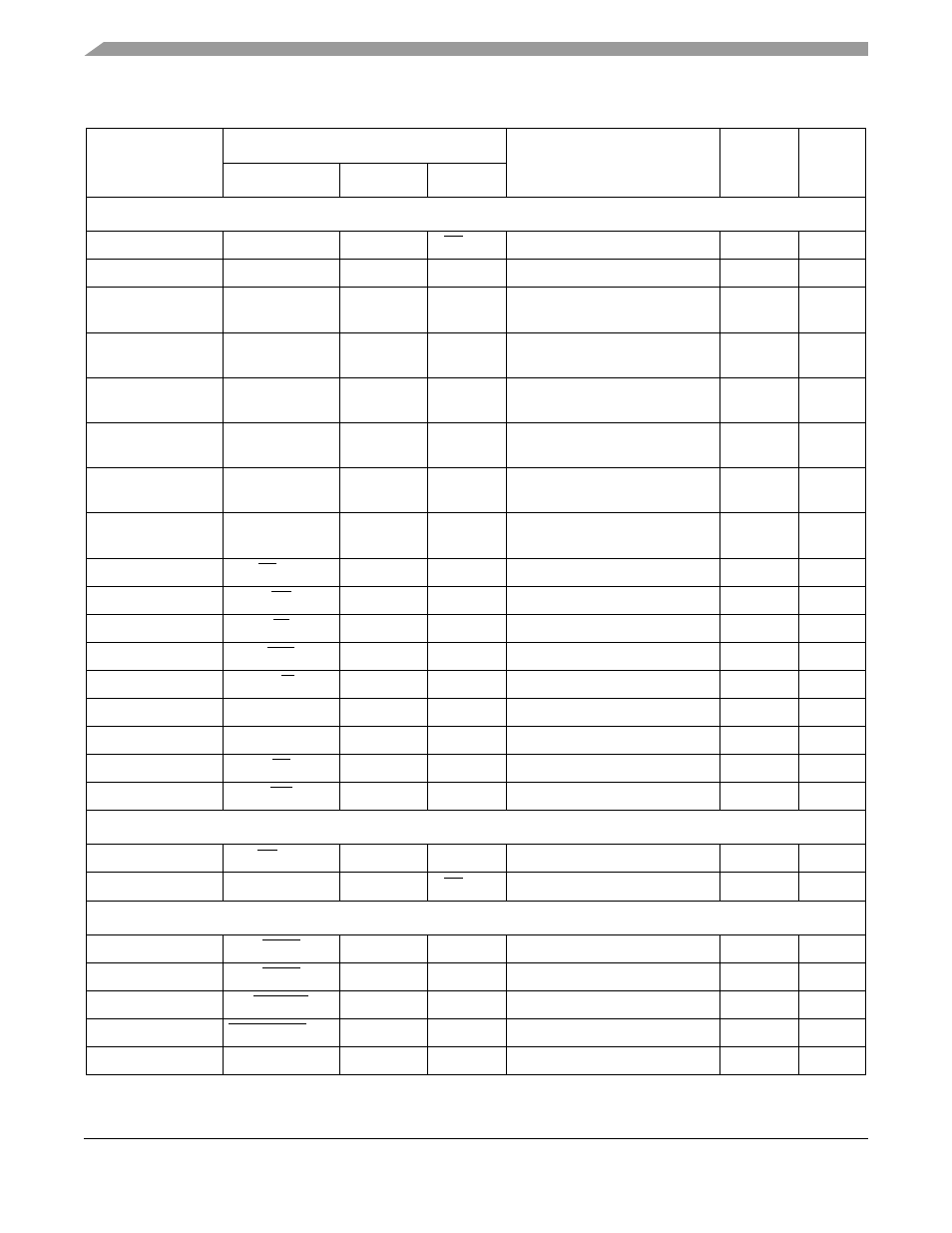

Table 14-3. MCF5282 Signals and Pin Numbers Sorted by Function (continued)

MAPBGA Pin

Pin Functions

Description

Primary

I/O

Internal

Pull-up

1

Primary

2

Secondary

Tertiary

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3