Motorola ColdFire MCF5281 User Manual

Page 717

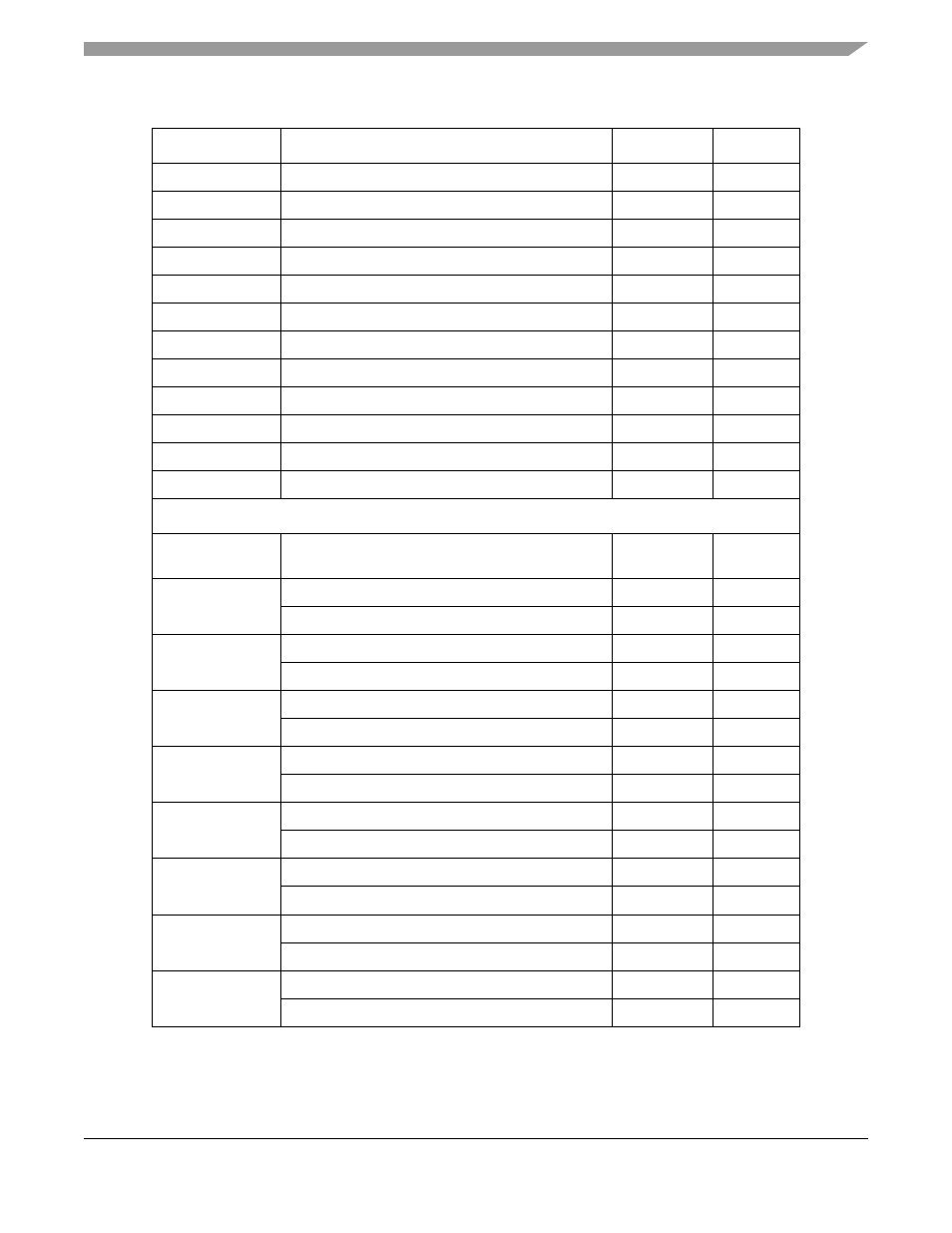

Register Memory Map

Freescale Semiconductor

A-5

IPSBAR + 0x14C

Byte Count Register 1

BCR1

32

IPSBAR + 0x150

DMA Status Register 1

DSR1

8

IPSBAR + 0x180

Source Address Register 2

SAR2

32

IPSBAR + 0x184

Destination Address Register 2

DAR2

32

IPSBAR + 0x188

DMA Control Register 2

DCR2

32

IPSBAR + 0x18C

Byte Count Register 2

BCR2

32

IPSBAR + 0x190

DMA Status Register 2

DSR2

8

IPSBAR + 0x1C0

Source Address Register 3

SAR3

32

IPSBAR + 0x1C4

Destination Address Register 3

DAR3

32

IPSBAR + 0x1C8

DMA Control Register 3

DCR3

32

IPSBAR + 0x1CC

Byte Count Register 3

BCR3

32

IPSBAR + 0x1D0

DMA Status Register 3

DSR3

8

UART Registers

IPSBAR + 0x200

UART Mode Register 0

2

UMR10,

UMR20

8

IPSBAR + 0x204

(Read) UART Status Register 0

USR0

8

(Write) UART Clock Select Register 0

UCSR0

8

IPSBAR + 0x208

(Read) Reserved

8

(Write) UART Command Register 0

UCR0

8

IPSBAR + 0x20C

(Read) UART Receive Buffer 0

URB0

8

(Write) UART Transmit Buffer 0

UTB0

8

IPSBAR + 0x210

(Read) UART Input Port Change Register 0

UIPCR0

8

(Write) UART Auxiliary Control Register 0

UACR0

8

IPSBAR + 0x214

(Read) UART Interrupt Status Register 0

UISR0

8

(Write) UART Interrupt Mask Register 0

UIMR0

8

IPSBAR + 0x218

(Read) Reserved

8

UART Baud Rate Generator Register 10

UBG10

8

IPSBAR + 0x21C

(Read) Reserved

8

UART Baud Rate Generator Register 20

UBG20

8

IPSBAR + 0x234

(Read) UART Input Port Register 0

UIP0

8

(Write) Reserved

8

Table A-3. Register Memory Map (continued)

Address

Name

Mnemonic

Size

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3