2 port qb digital i/o signals, 3 external trigger input signals, 4 multiplexed address output signals – Motorola ColdFire MCF5281 User Manual

Page 543: 5 multiplexed analog input signals, 2 port qb digital i/o signals -5

Queued Analog-to-Digital Converter (QADC)

Freescale Semiconductor

28-5

28.4.2.2

Port QB Digital I/O Signals

Port QB signals are referred to as PQB[3:0] when used as a 4-bit digital input/output port. In addition to

functioning as analog input signals, the port QB signals are also connected to the input of a synchronizer

during reads and may be used as general-purpose digital inputs when the applied voltages meet V

IH

and

V

IL

requirements.

Each port QB signal is configured as an input or output by programming the port data direction register

(DDRQB). The digital input signal states are read from the port QB data register (PORTQB) when

DDRQB specifies that the signals are inputs. The digital data in PORTQB is driven onto the port QB

signals when the corresponding bits in DDRQB specify output. See

Section 28.6.4, “Port QA and QB Data

Direction Register (DDRQA & DDRQB)

28.4.3

External Trigger Input Signals

The QADC has two external trigger signals, ETRIG2 and ETRIG1. Each external trigger input is

associated with one of the scan queues, queue 1 or queue 2. The assignment of ETRIG[2:1] to a queue is

made by the TRG bit in QADC control register 0 (QACR0). When TRG = 0, ETRIG1 triggers queue 1 and

ETRIG2 triggers queue 2. When TRG = 1, ETRIG1 triggers queue 2 and ETRIG2 triggers queue 1. See

Section 28.6.5, “Control Registers

28.4.4

Multiplexed Address Output Signals

In non-multiplexed mode, the QADC analog input signals are connected to an internal multiplexer which

routes the analog signals into the internal A/D converter.

In externally multiplexed mode, the QADC allows automatic channel selection through up to four external

4-to-1 multiplexer chips. The QADC provides a 2-bit multiplexed address output to the external

multiplexer chips to allow selection of one of four inputs. The multiplexed address output signals, MA1

and MA0, can be used as multiplexed address output bits or as general-purpose I/O when external

multiplexed mode is not being used.

MA[1:0] are used as the address inputs for up to four 4-channel multiplexer chips. Because the MA[1:0]

signals are digital outputs in multiplexed mode, the state of their corresponding data direction bits in

DDRQA is ignored.

28.4.5

Multiplexed Analog Input Signals

In external multiplexed mode, four of the port QB signals are redefined so that each represent four analog

input channels. See

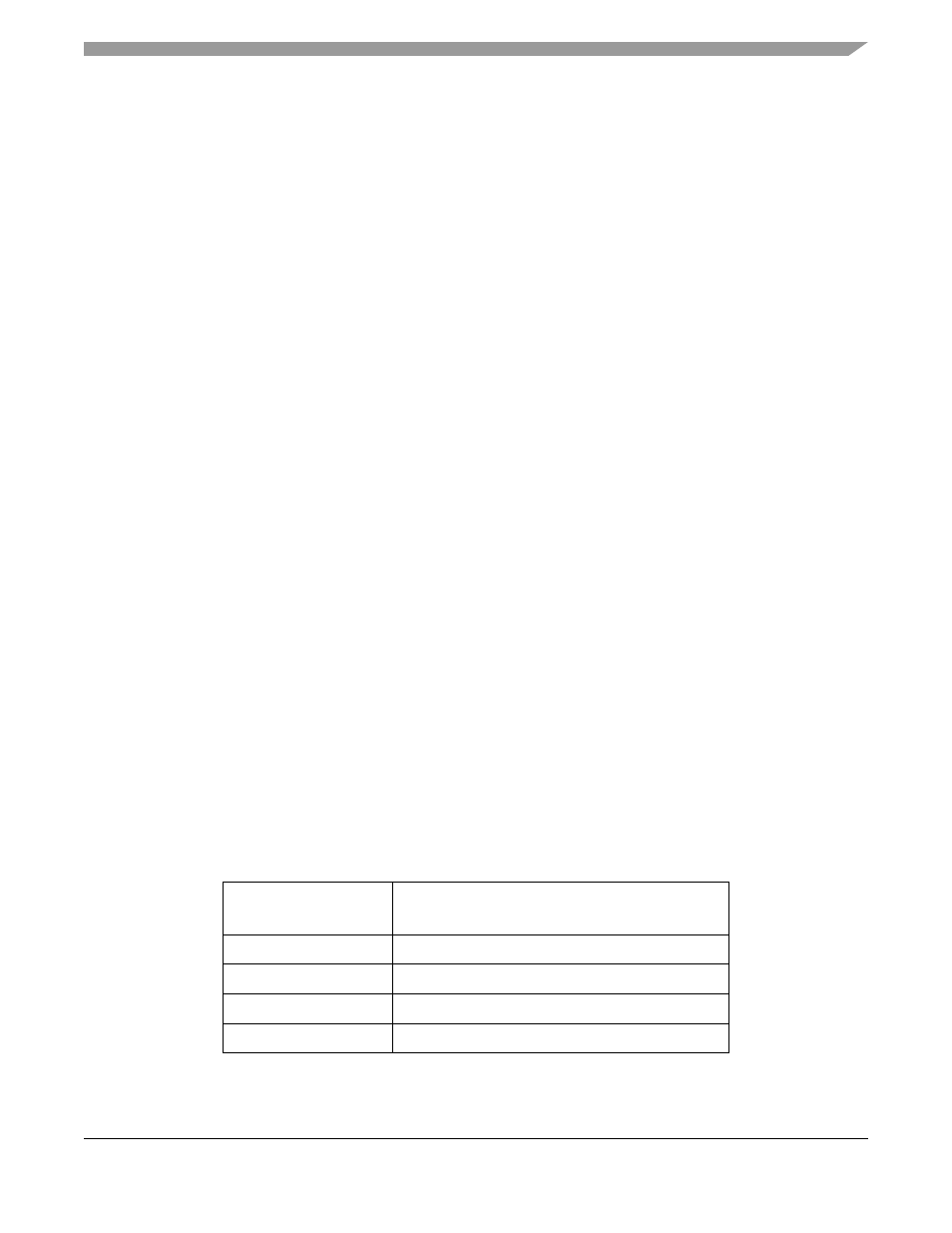

Table 28-1. Multiplexed Analog Input Channels

Multiplexed

Analog Input

Channels

ANW

Even numbered channels from 0 to 6

ANX

Odd numbered channels from 1 to 7

ANY

Even numbered channels from 16 to 22

ANZ

Odd numbered channels from 17 to 23

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3