16 pulse accumulator flag register (gptpaflg), 16pulse accumulator flag register (gptpaflg) -15 – Motorola ColdFire MCF5281 User Manual

Page 383

General Purpose Timer Modules (GPTA and GPTB)

Freescale Semiconductor

20-15

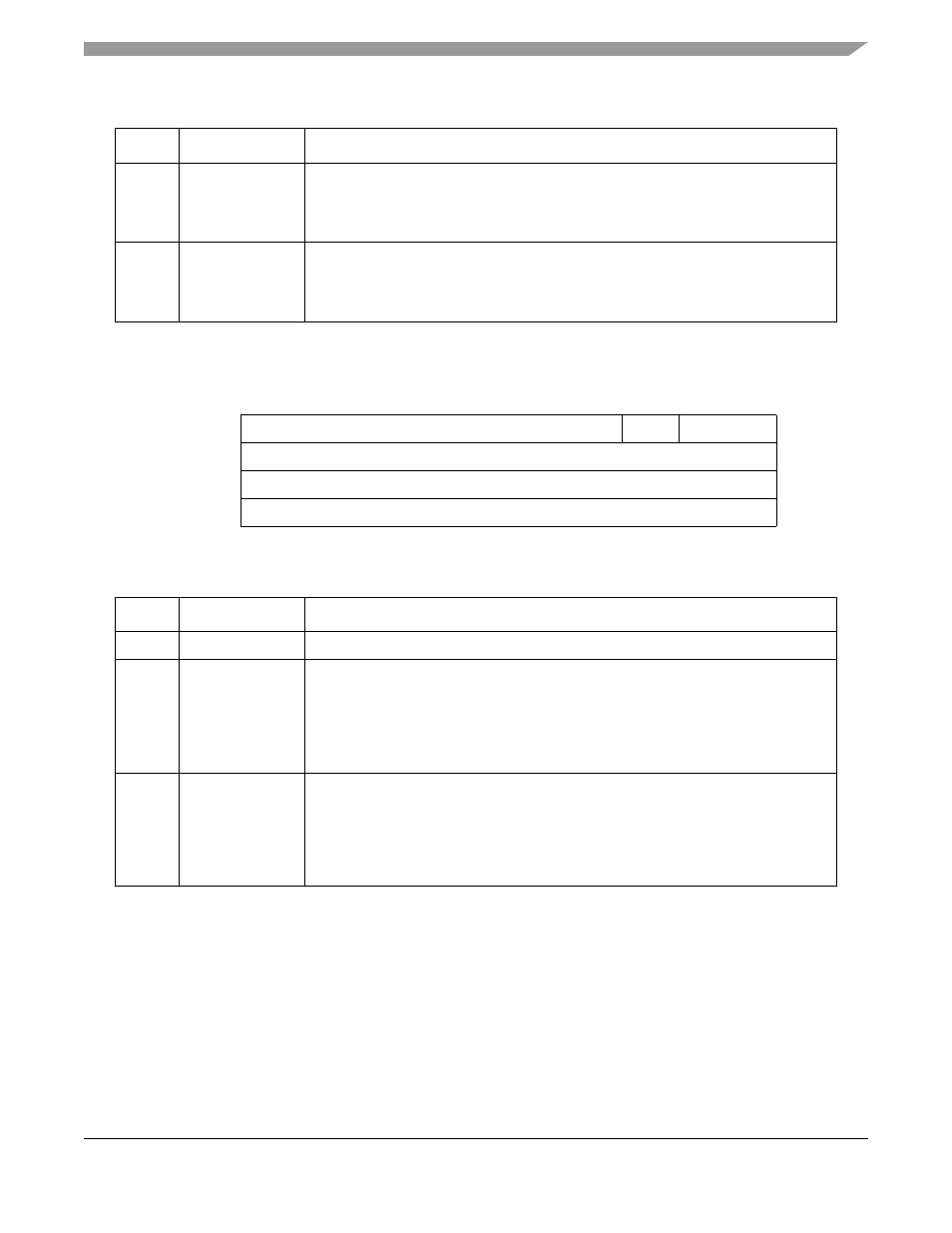

20.5.16 Pulse Accumulator Flag Register (GPTPAFLG)

NOTE

When the fast flag clear all enable bit, GPTSCR1[TFFCA], is set, any access

to the pulse accumulator counter registers clears all the flags in GPTPAFLG.

1

PAOVI

Pulse accumulator overflow interrupt enable. Enables the PAOVF flag to generate

interrupt requests.

1 PAOVF interrupt requests enabled

0 PAOVF interrupt requests disabled

0

PAI

Pulse accumulator input interrupt enable. Enables the PAIF flag to generate interrupt

requests.

1 PAIF interrupt requests enabled

0 PAIF interrupt requests disabled

7

2

1

0

Field

—

PAOVF

PAIF

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1A_0019, 0x1B_0019

Figure 20-18. Pulse Accumulator Flag Register (GPTPAFLG)

Table 20-19. GPTPAFLG Field Descriptions

Bit(s)

Name

Description

7–2

—

Reserved, should be cleared.

1

PAOVF

Pulse accumulator overflow flag. Set when the 16-bit pulse accumulator rolls over from

0xFFFF to 0x0000. If the GPTPACTL[PAOVI] bit is also set, PAOVF generates an

interrupt request. Clear PAOVF by writing a 1 to it. This bit is read anytime, write

anytime. (Writing 1 clears the flag; writing 0 has no effect.)

1 Pulse accumulator overflow

0 No pulse accumulator overflow

0

PAIF

Pulse accumulator input flag. Set when the selected edge is detected at the PAI pin.

In event counter mode, the event edge sets PAIF. In gated time accumulation mode,

the trailing edge of the gate signal at the PAI pin sets PAIF. If the PAI bit in GPTPACTL

is also set, PAIF generates an interrupt request. Clear PAIF by writing a 1 to it.

1 Active PAI input

0 No active PAI input

Table 20-18. GPTPACTL Field Descriptions (continued)

Bit(s)

Name

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3