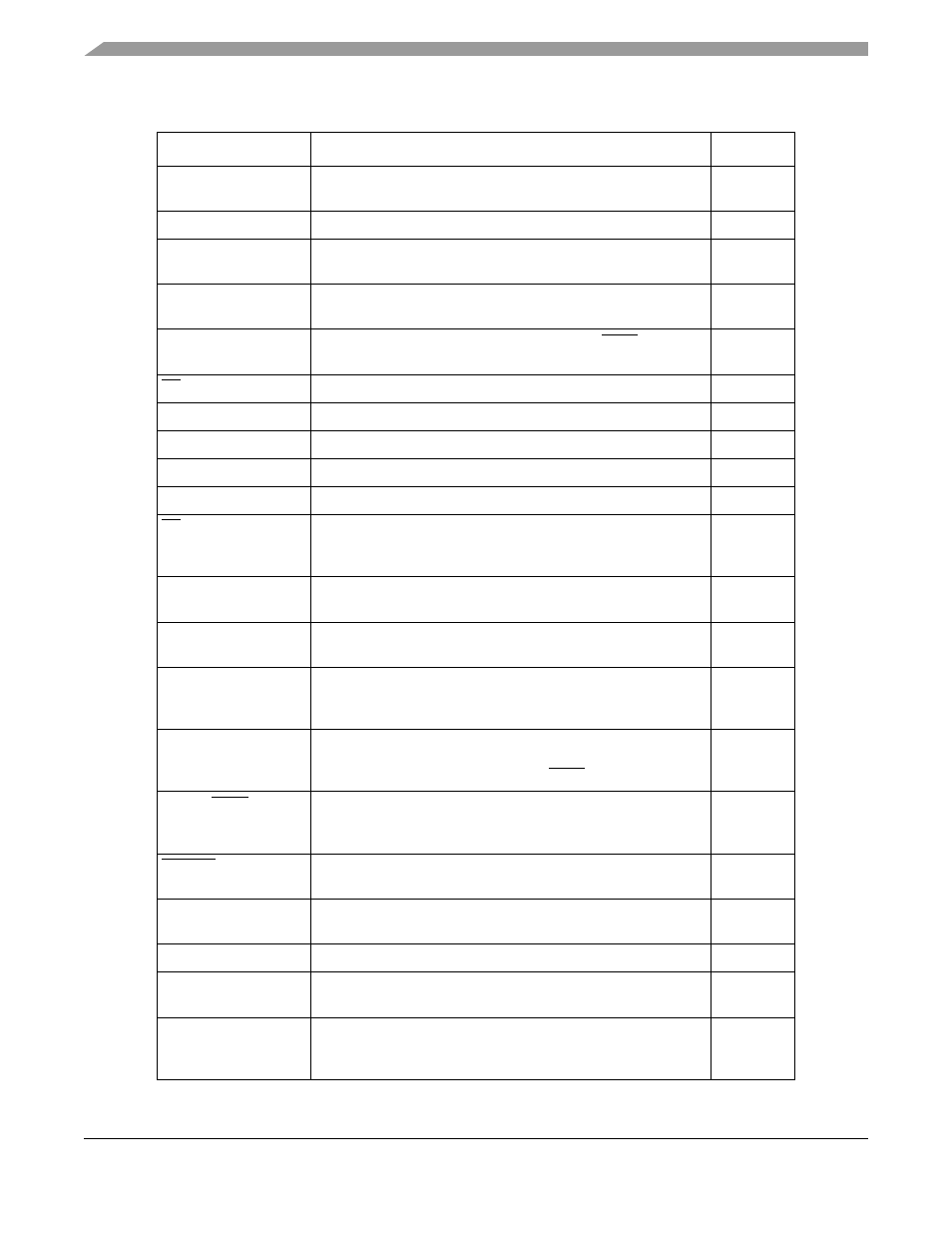

Table 14-2 – Motorola ColdFire MCF5281 User Manual

Page 248

Signal Descriptions

14-8

Freescale Semiconductor

Table 14-2. MCF5282 Alphabetical Signal Index

Abbreviation

Function

I/O

A[23:0]

Define the address of external byte, word, longword, and

16-byte burst accesses.

I/O

AN[0:3]/AN[W:Z]

Direct analog input ANn, or multiplexed input ANx.

I

AN[52:53]/MA[0:1]

Direct analog input ANn, or multiplexed output MAn. MAn

selects the output of the external multiplexer.

I/O

AN[55:56]/

TRIG[1:2]

Direct analog input ANn, or input TRIGn. TRIGn causes one of

the two queues to execute.

I

Breakpoint/

Test mode select

Signals a hardware breakpoint in debug mode (BKPT). Provides

information that determines JTAG test operation mode (TMS).

I

BS[3:0]

Define the byte lane of data on the data bus.

I/O

CANRX

Controller area network transmit data.

I

CANTX

Controller area network transmit data.

O

CLKMOD[1:0]

Clock mode select

I

CLKOUT

Reflects the system clock.

O

CS[6:0]

Programmed for a base address location and for masking

addresses, port size and burst capability indication, wait state

generation, and internal/external termination.

O

D[31:0]

Data bus. Provide the general purpose data path between the

MCU and all other devices.

I/O

DDATA[3:0]

Display captured processor addresses, data, and breakpoint

status.

O

DSO/TDO

Provides single-bit communication for debug module responses

(DSO). Provides serial data port for outputting JTAG logic data

(TDO).

O

DSI/TDI

Development serial clock for the serial interface to debug

module (DSCLK). Asynchronously resets the internal JTAG

controller to the test logic reset state (TRST).

I

DSCLK/TRST

Provides single-bit communication for debug module commands

(DSI). Provides serial data port for loading JTAG boundary scan,

bypass, and instruction registers (TDI).

I

DRAMW

Asserted to signify that a DRAM write cycle is underway.

Negated to indicate a read cycle.

O

DTIN[3:0]

Clock the event counter or provide a trigger to timer value

capture logic.

I/O

DTOUT[3:0]

Pulse or toggle on timer events.

I/O

ECOL

Asserted to indicate a collision.

Note: Not available on MCF5214 and MCF5216

I

ECRS

Asserted to indicate that the transmit or receive medium is not

idle.

Note: Not available on MCF5214 and MCF5216

I

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3