2 flexcan control register 0 (canctrl0), 2 flexcan control register 0 (canctrl0) -20, Table 25-9 describes the canctrl0 fields – Motorola ColdFire MCF5281 User Manual

Page 490

FlexCAN

25-20

Freescale Semiconductor

25.5.2

FlexCAN Control Register 0 (CANCTRL0)

describes the CANCTRL0 fields.

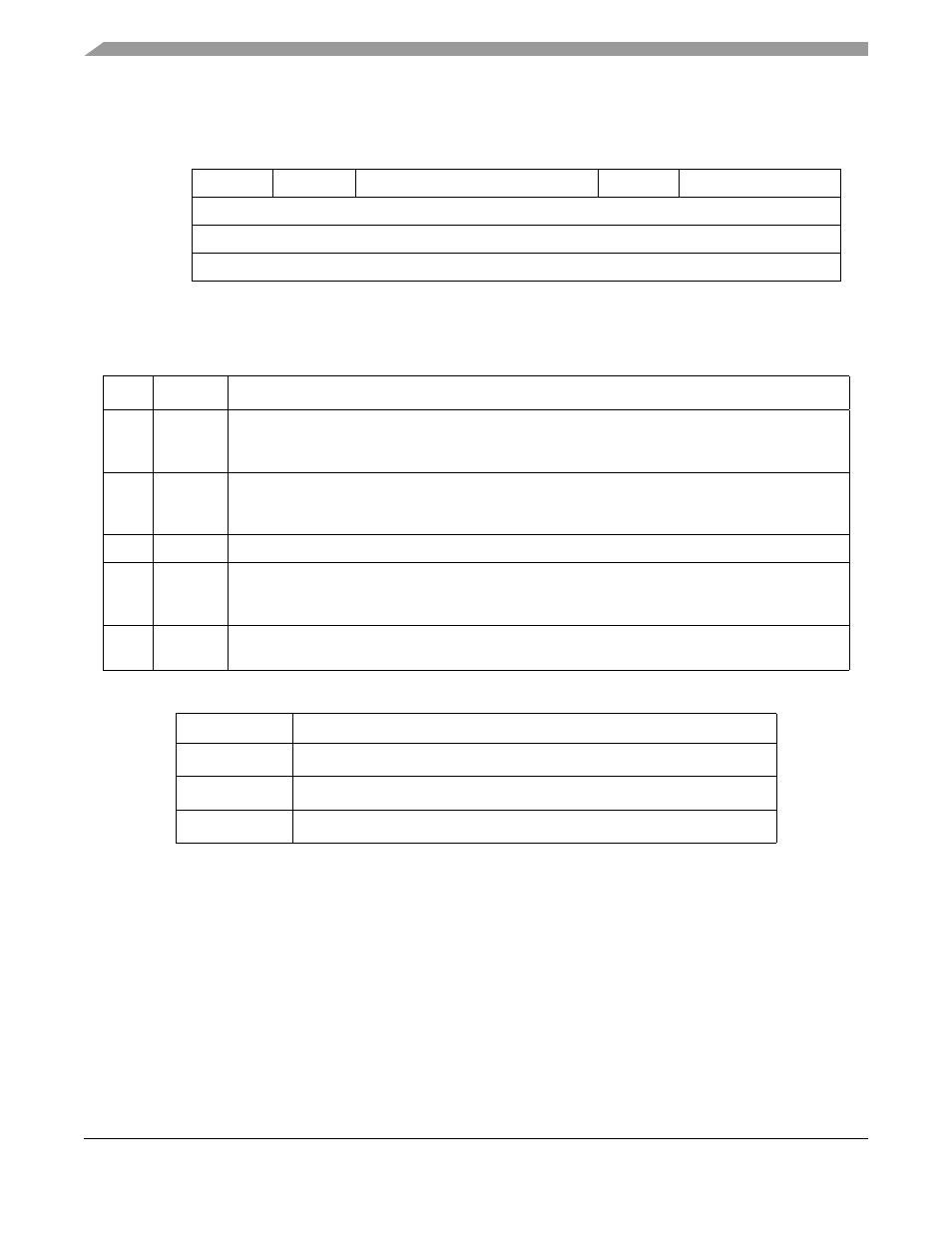

7

6

5

4

3

2

1

0

Field BOFFMSK

ERRMSK

—

RXMODE

TXMODE

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1C_0006

Figure 25-7. FlexCAN Control Register 0 (CANCTRL0)

Table 25-9. CANCTRL0 Field Descriptions

Bits

Name

Description

7

BOFFM-

SK

Bus off interrupt mask. The BOFF MASK bit provides a mask for the bus off interrupt.

0 Bus off interrupt disabled.

1 Bus off interrupt enabled.

6

ERRMSK

Error interrupt mask. The ERRMSK bit provides a mask for the error interrupt.

0 Error interrupt disabled.

1 Error interrupt enabled.

5–3

—

Reserved

2

RXMODE

Receive pin configuration control. This bit determines the polarity of the CANRX pin.

0 A logical ‘0’ is interpreted as a dominant bit; a logical ‘1’ is interpreted as a recessive bit.

1 A logical ‘1’ is interpreted as a dominant bit; a logical ‘0’ is interpreted as a recessive bit.

1–0

TXMODE

Transmit pin configuration control. This bit field controls the configuration of the CANTX pin. See

.

Table 25-10. Transmit Pin Configuration

TXMODE[1:0]

Transmit Pin Configuration

00

Full CMOS

1

; positive polarity (CANTX= 0 is a dominant level)

1

Full CMOS drive indicates that both dominant and recessive levels are driven by the chip.

01

Full CMOS

; negative polarity (CANTX = 1 is a dominant level)

1X

Open drain

2

; positive polarity

2

Open drain drive indicates that only a dominant level is driven by the chip. During a recessive

level, the CANTX pin is disabled (three stated), and the electrical level is achieved by external

pull-up/pull-down devices. The assertion of both Tx mode bits causes the polarity inversion to be

cancelled (open drain mode forces the polarity to be positive).

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3