B.7 changes between rev. 2.3 and rev. 3 – Motorola ColdFire MCF5281 User Manual

Page 744

Revision History

B-8

Freescale Semiconductor

B.7

Changes Between Rev. 2.3 and Rev. 3

Table 25-19/25-32 Changed BUFnI field description from “To clear an interrupt flag, first read the flag as a one, then write it

as a zero” to “To clear an interrupt flag, first read the flag as a one, then write it as a one.”

Chapter 33

Updated power consumption tables.

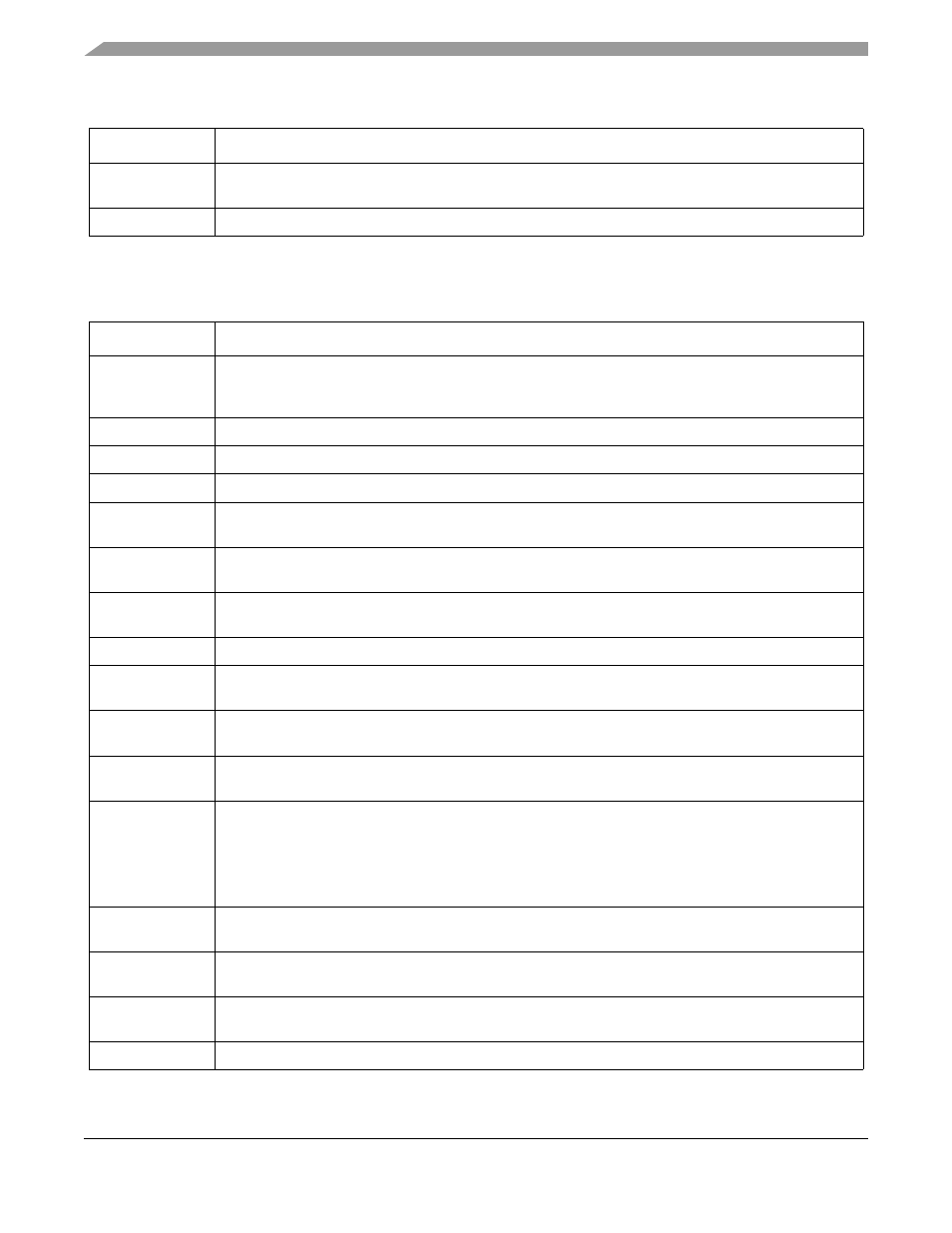

Table B-7. Rev. 2.3 to Rev. 3 Changes

Location

Description

Throughout

Added MCF5214 and MCF5216 to list of the devices supported in this document. These two devices are

the same as the MCF5282 except they do not have an FEC and have a rated frequency of 66 MHz.

Changed title of document.

Preface

Moved revision history to this appendix

Table 2-1/Page 2-4 Remove last sentence in C bit field description.

Table 2-3/Page 2-7 Change PC’s Written with MOVEC entry to “No”.

Section 2.5/Page

2-8

Change last bullet to “Use of separate system stack pointers for user and supervisor modes”

Section 2.5/Page

2-9

Change last sentence in fourth paragraph (step 2) to “The IACK cycle is mapped to special locations

within the interrupt controller's address space with the interrupt level encoded in the address."

Figure 3-6/Page

3-8

Add minus sign to the exponent so that it is “–(i + 1 – N)”.

Table 4-3/Page 4-5 Change reset value of ACR0, ACR1 to “See Section” since some of the bits are undefined after reset.

Figure 4-2/Page

4-6

Change CACR fields to R/W, since they may be read via the debug module.

Table 4-5/Page 4-8 For split instruction/data cache entry, swap text in parantheses in the description field. Instruction cache

uses the upper half of the arrays, while data cache uses the lower half.

Figure 4-3/Page

4-9

Change reset value of ACR: Bits 31-16, 14-13, 6-5, and 2 are undefined, and other bits are cleared.

Change ACR fields to R/W, since they may be read via the debug module.

Section

4.4.2.2/Page 4-9

Change note to:

NOTE

Peripheral (IPSBAR) space should not be cached. The combination

of the CACR defaults and the two ACRn registers must define the

non-cacheable attribute for this address space.

Figure 5-1/Page

5-2

Change RAMBAR fields to R/W, since they may be read via the debug module.

Table 5-1/Page 5-2 The PRI1/PRI2 text description does not match the table below it. It should be: “If a bit is set, CPU has

priority. If a bit is cleared, DMA has priority.”

Figure 6-3/Page

6-6

Changed FLASHBAR[WP] to read-only.

Table 6-2/Page 6-7 Changed bit description of FLASHBAR[WP] to read-only and that this bit is always set.

Table B-6. Rev. 2.2 to Rev. 2.3 Changes (continued)

Location

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3