1 memory interface, 1 local bus, 2 spi interface – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 73: 1 local bus 4.2.1.2 spi interface, Table 4-1, Spi chip select assignment, Functional description

Functional Description

ATCA-8310 Installation and Use (6806800M72E)

73

4.2.1

Memory Interface

The Freescale P4080 provides an on-chip DDR3 compliant memory controller with the

following features:

Programmable timing supporting DDR2 and DDR3 SDRAM

Two channel 64-bit data interface, supporting interleaving

Full ECC support

4.2.1.1

Local Bus

The Freescale P4080 provides an enhanced local bus controller (eLBC).

The Glue-Logic FPGA is connected to LCS3# and configured as a 8 Bit device. LCS0-2# are

connected to the FPGA as spare signals. LCS4# - 7# are not used.

4.2.1.2

SPI Interface

The Freescale P4080 includes a full duplex four-wire SPI interface. The SPI interface can

support up to four separate SPI devices. The P4080 SPI interface is routed to the ACS8520B

linecard PLL, and to the SPI-boot Flashes. The following table shows the P4080 chip select

assignments for the SPI devices.

4.2.1.2.1 Boot Flash

On the ATCA-8310, two SPI Flash devices are used as boot devices for the service processor.

The flash devices used will be Atmel AT25321 with a capacity of 32MBit.

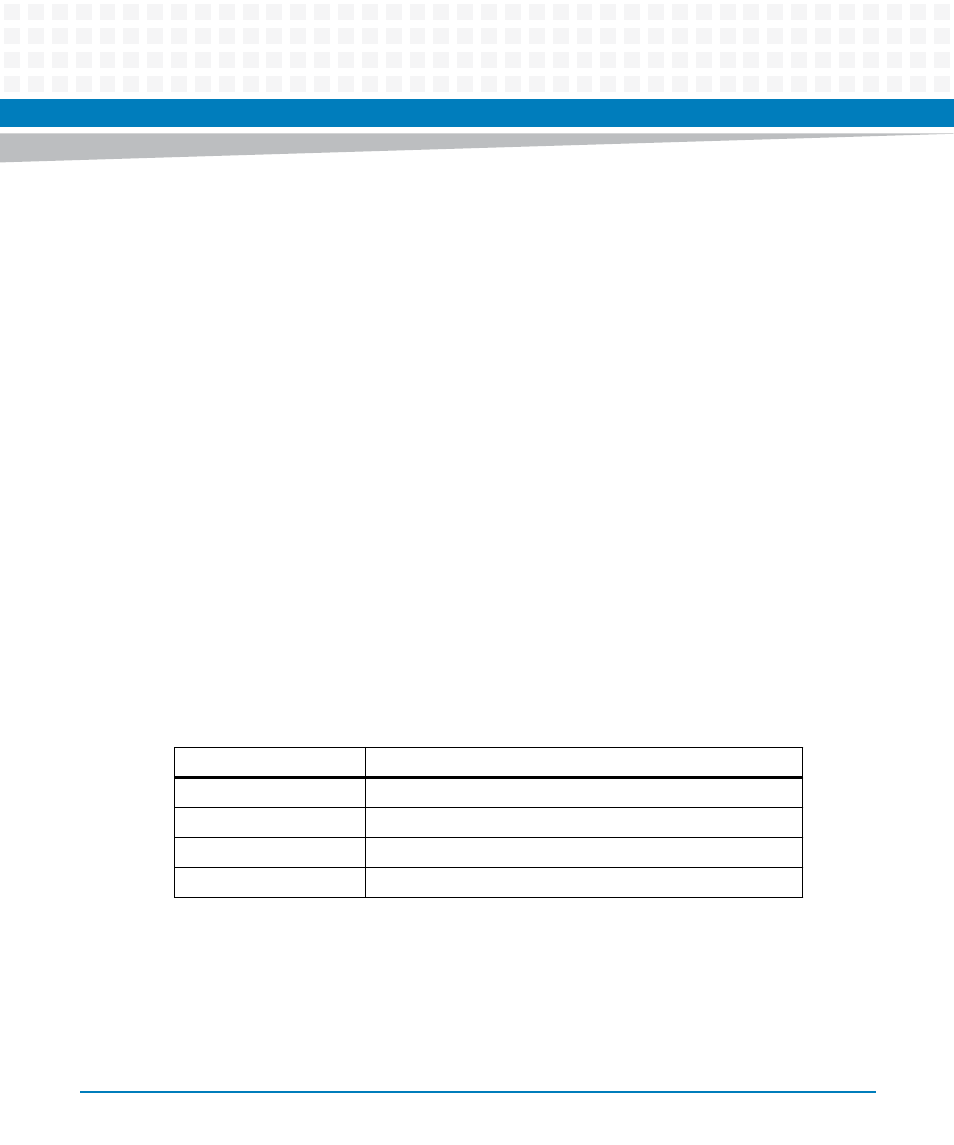

Table 4-1 SPI Chip Select Assignment

SPI Chip Select

Value

CS0

SPI-Boot Flash

CS1

SPI-backup Boot Flash

CS2

ACS8520B

CS3

Terminal Server