Table 8-79, Ipmc watchdog timeout register, Table "ipmc watchdog timeout register" on – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 305: Is s, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

305

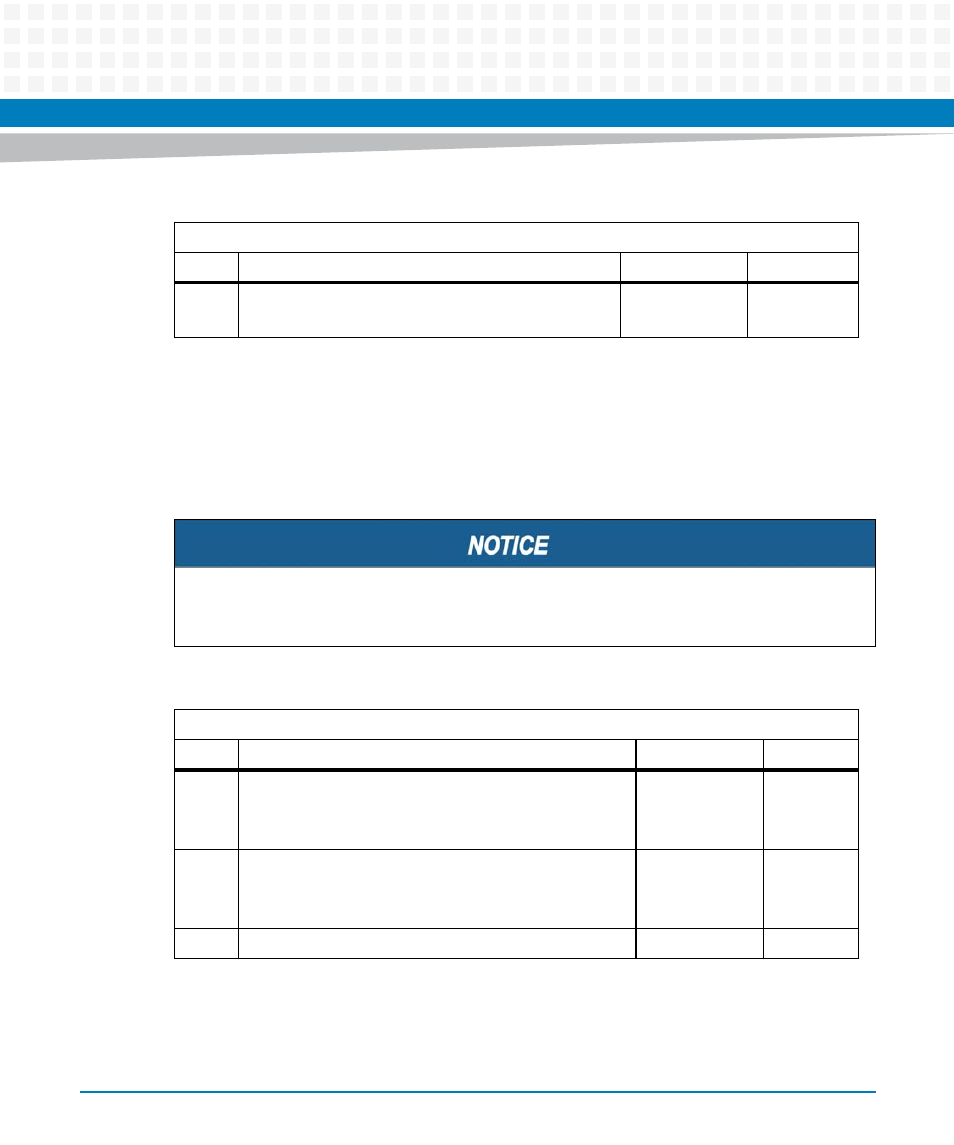

8.2.2.3.14 IPMC Watchdog Timeout Register

The IPMC SW set the corresponding bit to signal an IPMC watchdog timeout event. When the

IPMC Watchdog Timeout bit is set from low to high, the corresponding bits in

Watchdog Timeout Register" on page 302

and

Table "OS IPMC Watchdog Timeout Register" on

are set.

7

IPMC_RST_ REQ_ Payload Reset from IPMC.

1: Reset occurred

PWR_GOOD:0

IPMC: r/w1c

Table 8-78 IPMC Reset Source Indication Register (continued)

Address: 0x10

Bit

Description

Default

Access

IPMC needs to clear the IPMC watchdog timeout bit to arm IPMC watchdog timeout event

recognition.

Table 8-79 IPMC Watchdog Timeout Register

Address: 0x11

Bit

Description

Default

Access

0

IPMC Watchdog Timeout:

0: No IPMC Watchdog Timeout

1: IPMC Watchdog Timeout occurred

PWR_GOOD:0

IPMC: r/w

1

IPMC Pre-Timeout

0: No IPMC Pre-Timeout

1: IPMC Pre-Timeout occurred

PWR_GOOD:0

IPMC: r/w

7:2

Reserved

0

r