Table 8-5, Jtag update register, Table 8-6 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 249: Status debug switches, dmc base id register, Cpld and fpga, 2 jtag update register, 3 status registers

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

249

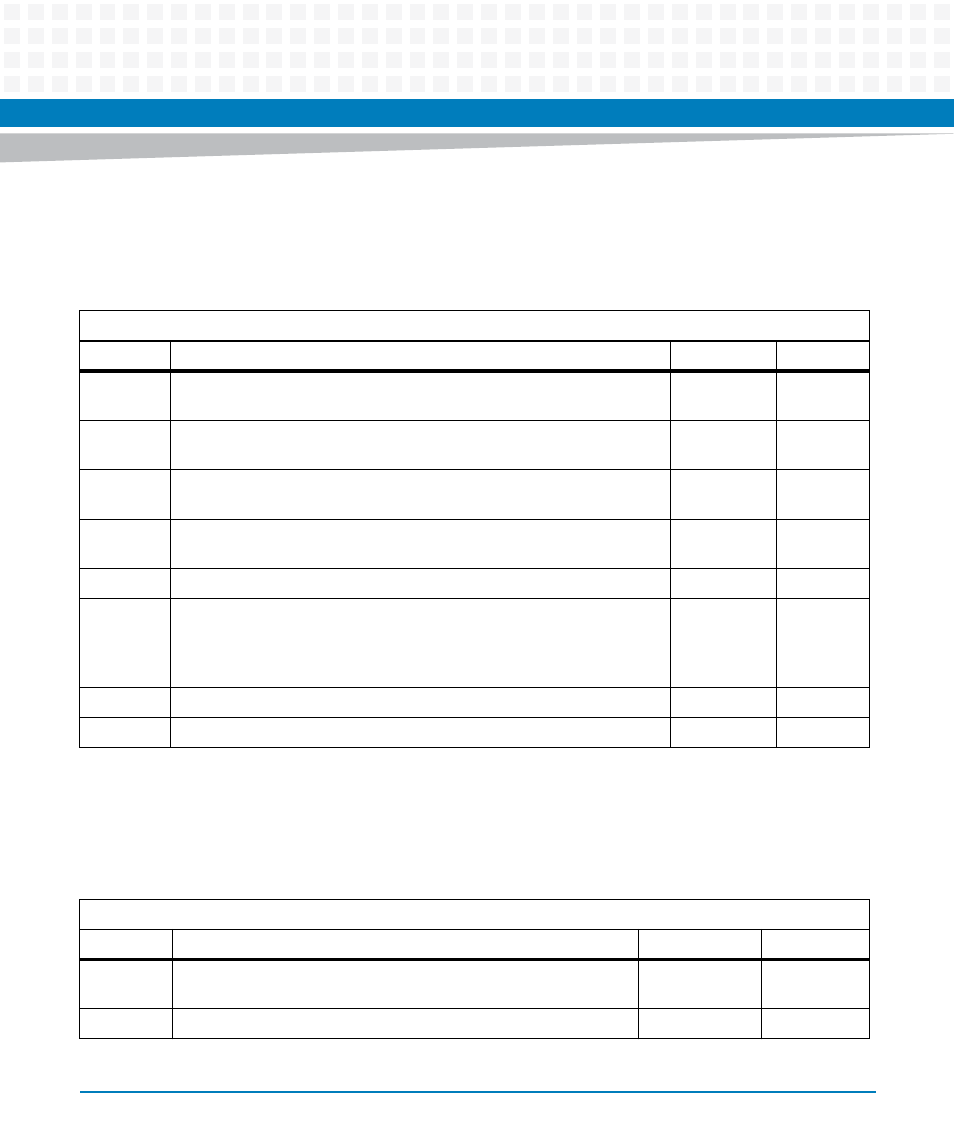

8.1.2.2.2 JTAG Update Register

The JTAG Update Register can be used to update the CPLD running a STAPL player on SPP.

8.1.2.2.3 Status Registers

Table 8-5 JTAG Update Register

CPLD Address: 0x01

Bit

Description

Default

Access

0

TDO output data. Connected to dedicated JTAG pin TDI.

Note: Only used when output enabled (bit 5 set).

0

SPP: r/w

1

TCK output data. Connected to dedicated JTAG pin TCK

Note: Only used when output enabled (bit 5 set).

0

SPP r/w

2

TMS output data. Connected to dedicated JTAG pin TMS

Note: Only used when output enabled (bit 5 set).

0

SPP: r/w

3

Enable bit.

Note: Not connected to external pin.

0

SPP: r/w

4

TRST bit.

0

SPP: r/w

5

Output enable:

0: TCK, TMS and TDO are tristate. CPLD_UPDATE_EN driven low

1: TCK, TMS and TDO are driving the values corresponding to bits [2:0].

CPLD_UPDATE_EN driven high.

0

SPP: r/w

6

Read TDI. Connected to dedicated JTAG pin TDO

Ext: TDO

SPP: r

7

Reserved

0

r

Table 8-6 Status Debug Switches, DMC Base ID Register

CPLD Address: 0x02

Bit Description

Default

Access

3:0

Signal Level of switches SWITCH[4:1]. Read bit 1 when

corresponding switch is open.

ext.

r

7:4

DMC Base Identification. Level of DMC_ID[3:0] signals

ext.

r