Table 6-10, Post tests and description, U-boot – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 195

U-Boot

ATCA-8310 Installation and Use (6806800M72E)

195

The default is to execute long POST.

Each time a sing POST test is started, an IPMI boot progress event is issued to the IPMI

controller. When the particular event fails, the same event is sent as POST error.

The overall result of the POST is encoded in the u-boot variable "post_result", which is an XML

like string of tokens of the format:

[

testName ist the name of the test, errorId is an error identifier.

Before a component is tested system firmware progress event message is sent to the IPMC. The

OEM specific event data byte 2 is set to 0xfd, event data byte 3 denotes the component being

tested (seefollowing table).

If the test fails, a post error message is sent with the same data bytes.

The following table lists all tests and the associated error identifiers:

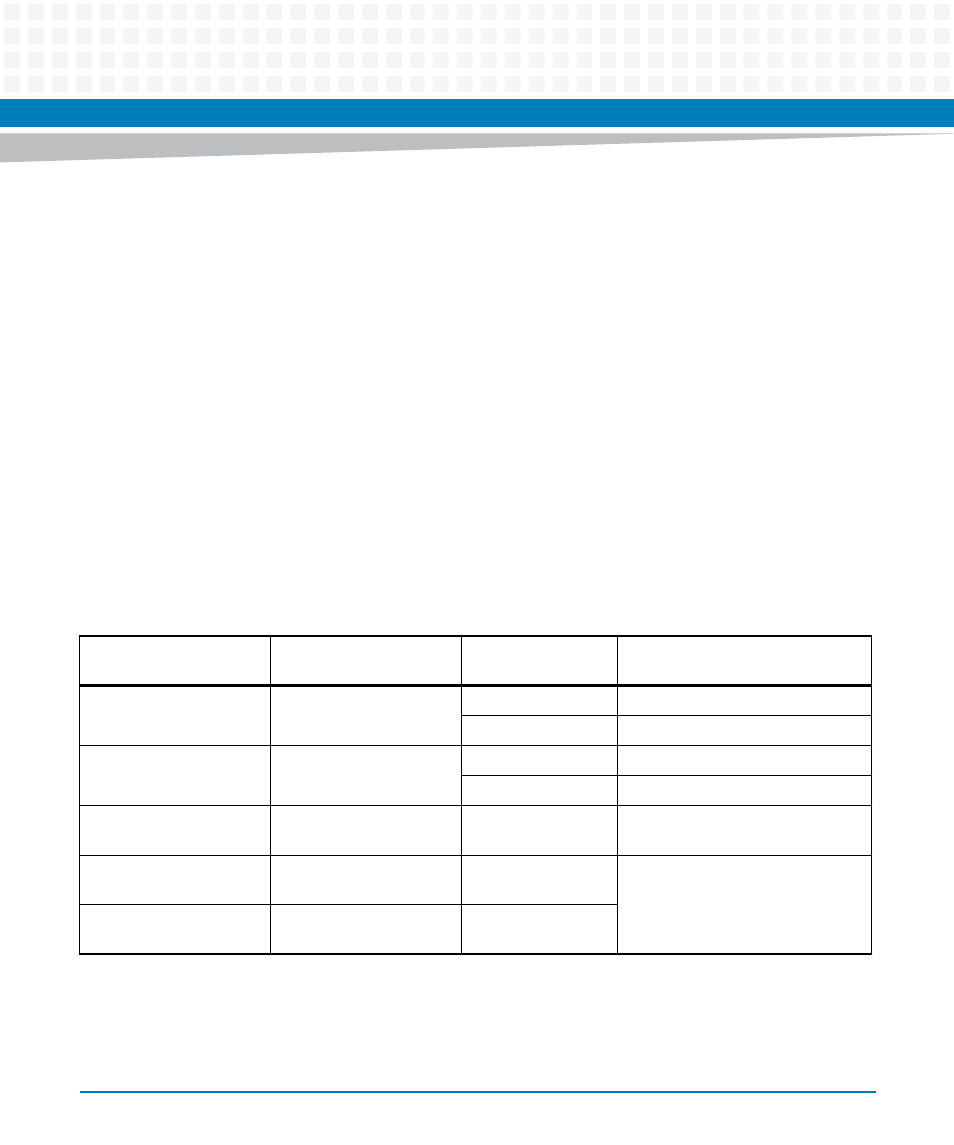

Table 6-10 POST Tests and Description

Test Name / Event Data

Byte 3

Description

errorId

Description

FPGA / 0x1f

Performs test on the glue

logic FPGA

ID check

Bad ID register content

walking-one

Walking one bit test failed

CPLD / 0x1f

Performs test on the

power-up CPLD

IOERR

Access to CPLD failed (SPI bus error)

REGERR

Register read/write test failed

BASE_SWITCH / 0x25

Performs test on the base

switch (Marvell 88e6161)

ID check

Wrong device ID read (MDIO access

problem)

I2C CTRL1 / 0x0A

Performs tests on P4080

I2C bus 1

Missing:

A specific device was not detected

on the bus.

I2C CTRL2 / 0x0A

Performs tests on P4080

I2C bus 2

Missing: