Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 378

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

378

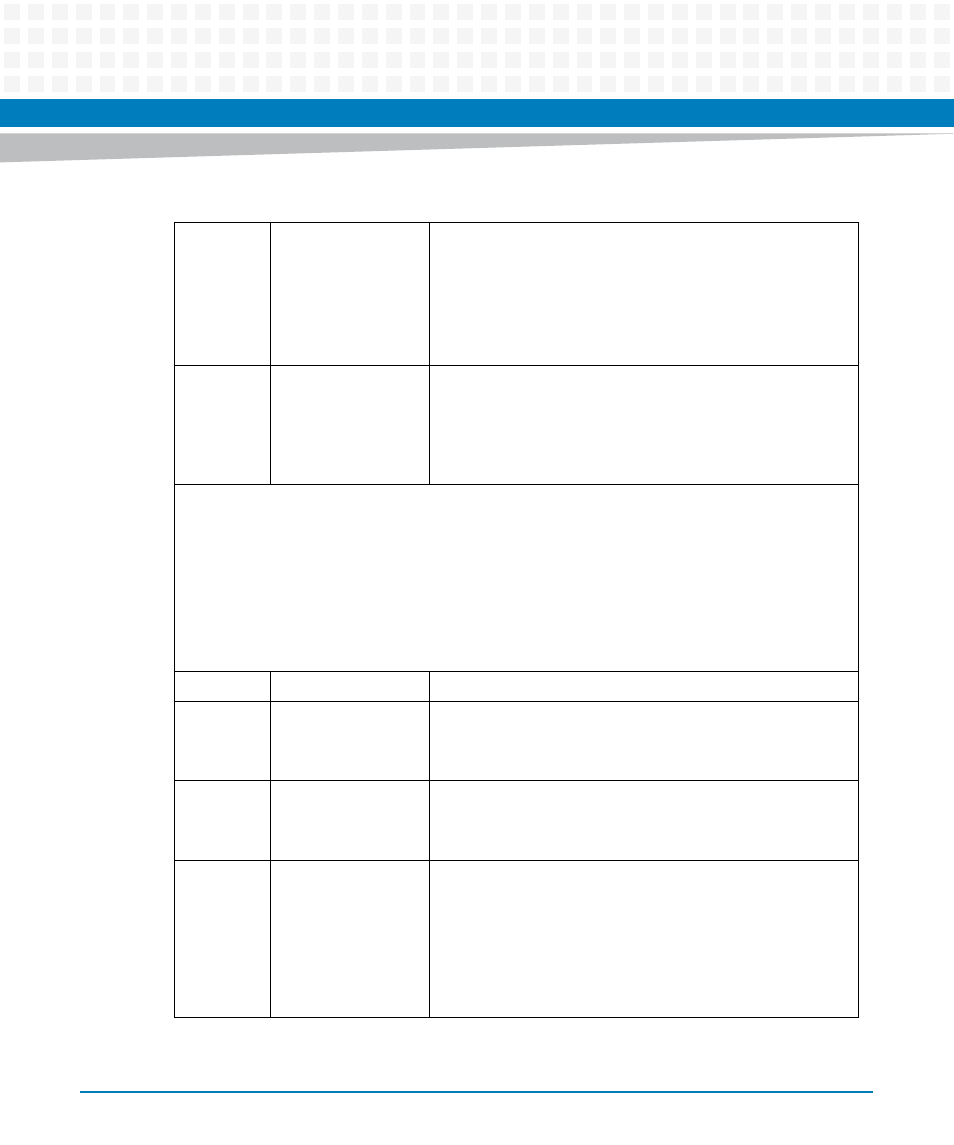

0x98

DspPhyResNmiCtrlR

eg

DSPand Phy Reset and Dsp NMI Control Register (32bit) [Hw:

syn, WAck1, RAck1]

This register is used to control the reset pins of the 10 TI

Tomahawk DSPs (TMS320TCI6486) and the RGMII Phy device.

For the DSPs the boot mode can be selected

0x9C

DspResNmiCtrlReg

DSP Local Reset and NMI Control Register (16bit) [Hw: syn,

WAck1, RAck1]

This register is used to control the local reset and NMI pins to

10 TI Tomahawk DSPs (TMS320TCI6486).

DSP Status and Interrupt Block (DspStaIntBlk) [Hw: Cy0]

This Block is connected to the status lines (DSP_RESETSTAT_N, DSP_BOOTACTIVE) and interrupt

lines (DSP_HOUT, DSP_WDOUT)

of each DSP. The status of all lines can be read from the Status and Interrupt Monitor Registers. DSP

interrupts (DSP_HOUT, DSP_WDOUT)

are forwarded to the controller cpu.

Access via SPI- bus from GlueFpga (occupies 256 Byte addressarea), hereof assigned to this block:

A0...AF

Address

Acronym

Description

0xA0

DspBootStaReg

DSP Boot Status Register (16bit) [Hw: syn , WAck1, RAck1]

This register monitors the Boot status of 10 DSPs.

0xA2

DspResStaReg

DSP Reset Status Register (16bit) [Hw: syn, WAck1, RAck1]

This register monitors the Reset status of 10 DSPs.

0xA4

DspWdgStaReg

DSP Watchdog Interrupt Status Register (16bit ) [Hw: syn ,

WAck1, RAck1]

This register monitors the Watchdog Interrupt status of 10

DSPs. If a Watchdog Interrupt occurs, the respective bit is set.

It can be reset by writing the respective bit in

DspWdgStaResReg.

Table 8-174 Logic DSP FPGA Register Overview (continued)