Table 8-194, Test frame count register, Table 8-195 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 401: Supplemental test pattern error count register, Cpld and fpga, 7 supplemental test pattern error count register, 8 crc error count register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

401

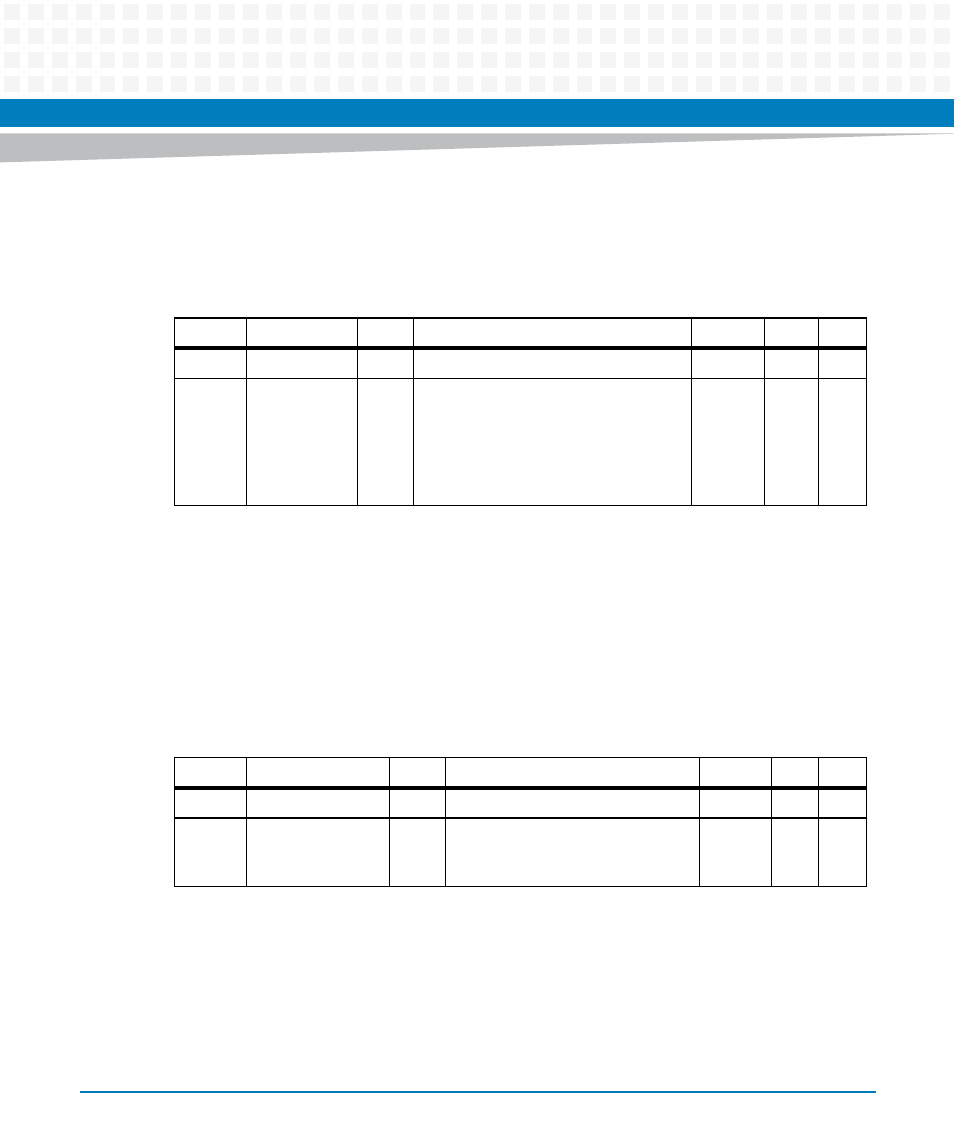

This register indicates the number of 125 μs frames since starting the frame sync counting by

Des2TsipErrCntCtrlReg:FrameCntStart bit. During 125 μs one SerDes frame is received. Each

frame contains a static test pattern and a CRC checksum.

8.4.2.5.7 Supplemental Test Pattern Error Count Register

Address: 0x8C, SupplTstPatErrCntReg

Width: 32 bit

This register indicates the number of the test pattern errors since starting the static pattern

reception by the pErrCntCtrlReg:SupplTstPatErrCntStart bit. The counter sticks at 0xFFFF_FFFF.

8.4.2.5.8 CRC Error Count Register

Address: 0x90, CrcErrCntReg

Width: 32 bit

Table 8-194 Test Frame Count Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...24

-

-

reserved

undef

-

-

23...0

TstFrameCnt

R

This bitfield indicates the time elapsed

since the start of frame counting by

setting the

Des2TsipErrCntCtrlReg:FrameCntStart

bit (value x 125 μs). The counter sticks

at 0xFFFFFF.

0x0

F

F

Table 8-195 Supplemental Test Pattern Error Count Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...24

-

-

reserved

undef

-

-

23...0

SupplTstPatErrCnt

R

This register indicates the number

of erroneous pattern. The error

counter sticks at 0xFFFFFF.

0x0

F

F