Table 8-50, Receiver buffer register (rbr) if dlab=0, Table 8-51 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 277: Transmitter holding register (thr) if dlab=0, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

277

In non-FIFO mode, this register holds the character received by the UART's Receive Shift

Register. If fewer than eight bits are received, the bits are right-justified and the leading bits are

zeroed. Reading the register empties the register and resets the Data Ready (DR) bit in the Line

Status Register to zero. Other (error) bits in the Line Status Register are not cleared. In FIFO

mode, this register latches the value of the data byte at the top of the FIFO.

- Transmitter Holding Register (THR)

This register holds the next data byte to be transmitted. When the Transmit Shift Register

becomes empty, the contents of the Transmit Holding Register are loaded into the shift

register and the transmit data request (TDRQ) bit in the Line Status Register is set to one.

In FIFO mode, writing to THR puts data to the top of the FIFO. The data at the bottom of the

FIFO is loaded to the shift register when it is empty.

- Interrupt Enable Register (IER)

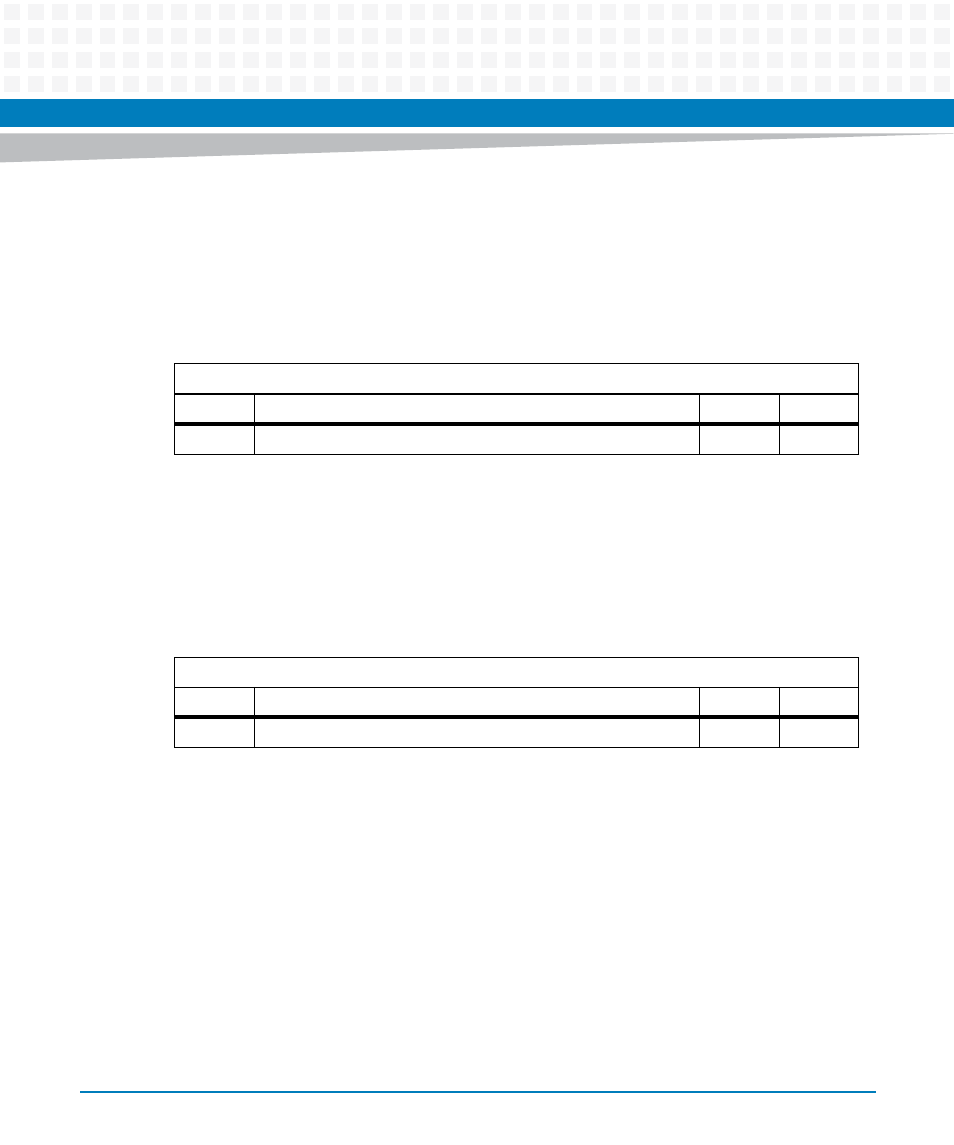

Table 8-50 Receiver Buffer Register (RBR) if DLAB=0

IO Address: Base

Bit

Description

Default

Access

7.0

Receiver Buffer register(RBR)

Undef.

GPP: r

Table 8-51 Transmitter Holding Register (THR) if DLAB=0

IO Address: Base

Bit

Description

Default

Access

7.0

Transmitter Holding register(THR)

Undef.

GPP: w