Table 8-188, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 396

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

396

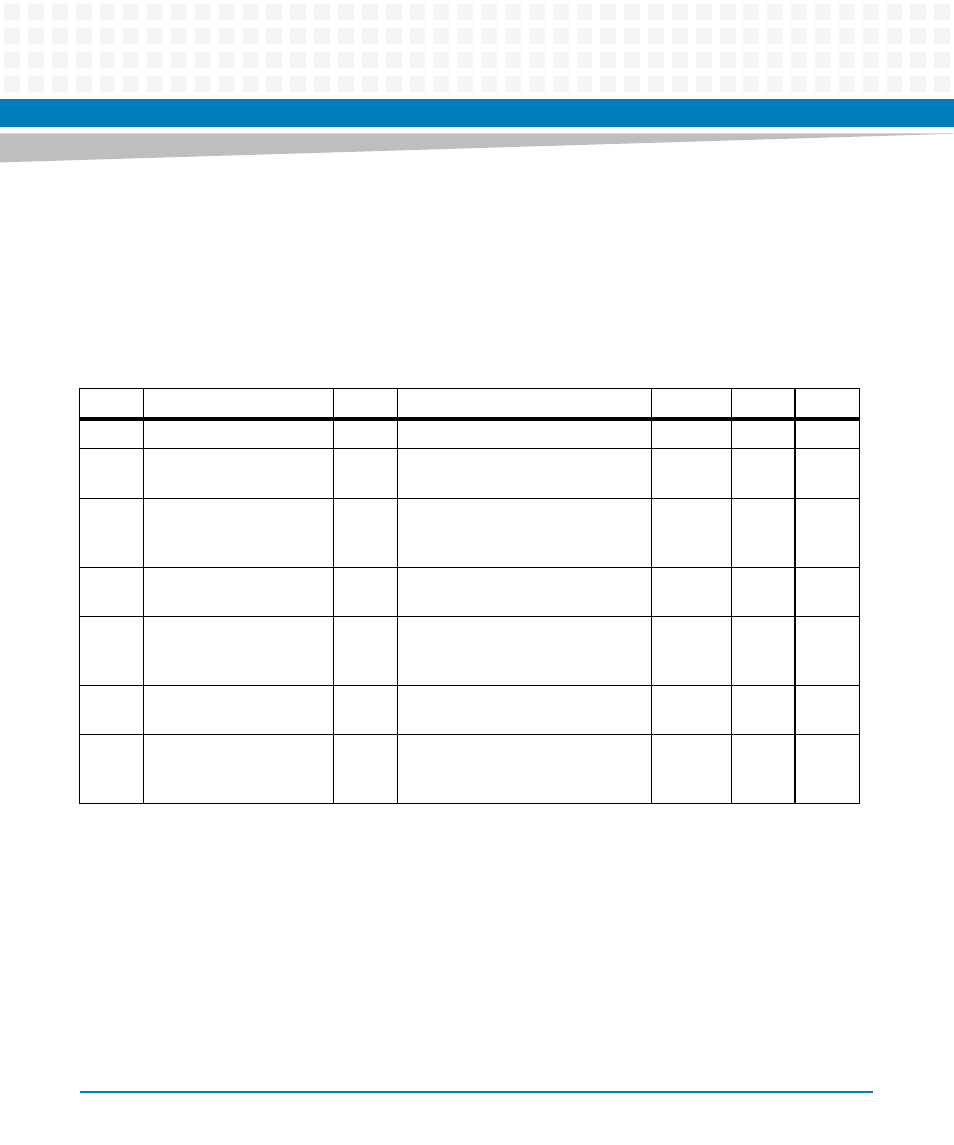

8.4.2.4.4 Supplemental Test Pattern, CRC and Disparity Generator Control Register

Address: 0x74, SupplTstPatCrcDispGenCtrlReg

Width: 8 bit

This registers controls test pattern, CRC and Disparity transmission

8.4.2.5

Deserializer to TSIP Allocater Block (Des2TsipBlk)

Resets:

Pwr = Power On Reset

Soft = Soft Reset

The Des2TsipBlk allocates data from the 16 bit parallel interface of the SerDes IP block to 60

TSIP-links. The received supplemental channel test pattern data can be read by using the

registers of this block. Furthermore the CRC status signals from the SerDes IP Block are

evaluated and CRC errors are counted and indicated.

Table 8-188 Supplemental Test Pattern, CRC and Disparity Generator Control Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...6

-

-

reserved

undef

-

-

5

SupplTstPatGenContErrPr

vk

RW

0b1: SupplTstPatGenContErrPrvk,

errors are inserted continuously

0b0

X

X

4

SupplTstPatGenSingleErr

Prvk

RW

0b1: SupplTstPatGenSingleErrPrvk,

one error is inserted when the bit

changes from 0 to 1

0b0

X

X

3

CrcGenConErrPrvk

RW

0b1: CrcGenContErrPrvk, errors are

inserted continuously

0b0

X

X

2

CrcGenSingleErrPrvk

RW

0b1: CrcGenSinglErrPrvk, one error

is inserted when the bit changes

from 0 to 1

0b0

X

X

1

DispGenContErrPrvk

RW

0b1: DispGenContErrPrvk, errors

are inserted continuously

0b0

X

X

0

DispGenSingleErrPrvk

RW

0b1: DispGenSingleErrPrvk, one

error is inserted when the bit

changes from 0 to 1

0b0

X

X