Table 8-7, Status dmc 1 id and dmc 2 id register, Table 8-8 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 250: Gpp status signals part 1register, Table 8-9, Gpp status signals part 2register, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

250

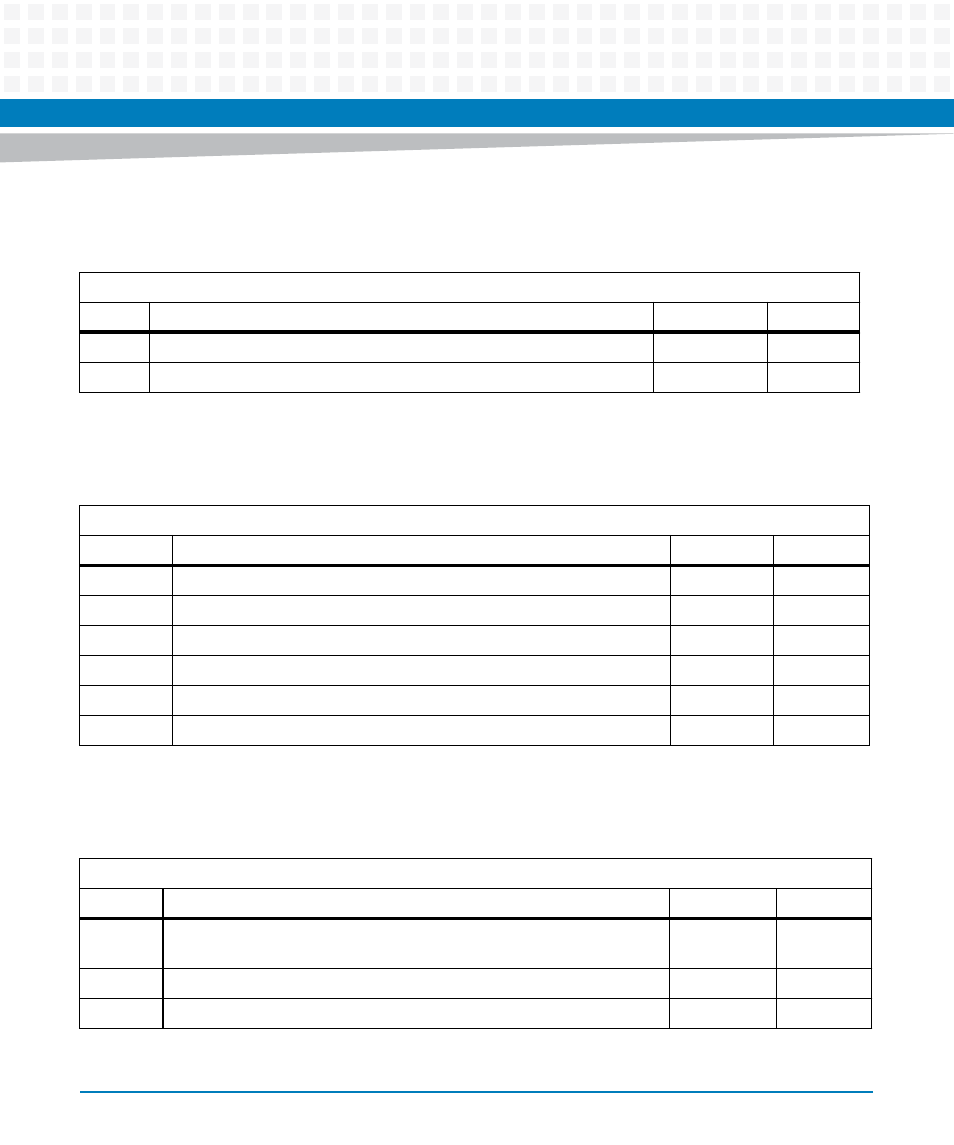

Table 8-7 Status DMC 1 ID and DMC 2 ID Register

CPLD Address: 0x03

Bit Description

Default

Access

3:0

DMC 1 Identification. Level of DMC1_ID[3:0] signals

ext.

r

7:4

DMC 2 Identification. Level of DMC2_ID[3:0] signals

ext.

r

Table 8-8 GPP Status Signals Part 1Register

CPLD Address: 0x04

Bit

Description

Default

Access

0

GPP present Signal. Level of GPP_PRESENT_ Signal.

ext.

r

1

Ibex Peak PME_N. Level of PCH_PME_ Signal.

ext.

r

2

Ibex Peak SLP_LAN_N/GPIO29. Level of PCH_SLP_LAN_ Signal.

ext.

r

5:3

Ibex Peak SLP_S[5:3]. Level of PCH_SLP_S_[5:3] Signals.

ext.

r

6

Ibex Peak SLP_M_N. Level of PCH_SLP_M_ Signal.

ext.

r

7

Ibex Peak SUS_STAT_N/GPIO61. Level of PCH_SUS_STAT_ Signal.

ext.

r

Table 8-9 GPP Status Signals Part 2Register

CPLD Address: 0x05

Bit

Description

Default

Access

0

Ibex Peak SUS_PWR_DN_ACK/GPIO30. Level of PCH_SUS_PWR_DN_ACK

Signal.

ext.

r

1

Ibex Peak SATA5GP/GPIO49. Level of PCH_TEMP_ALERT_ Signal.

ext.

r

7:2

Reserved

0

r