Table 8-139, Spp interrupt group status registers, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 333: 35 spp interrupt register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

333

8.2.2.3.35 SPP Interrupt Register

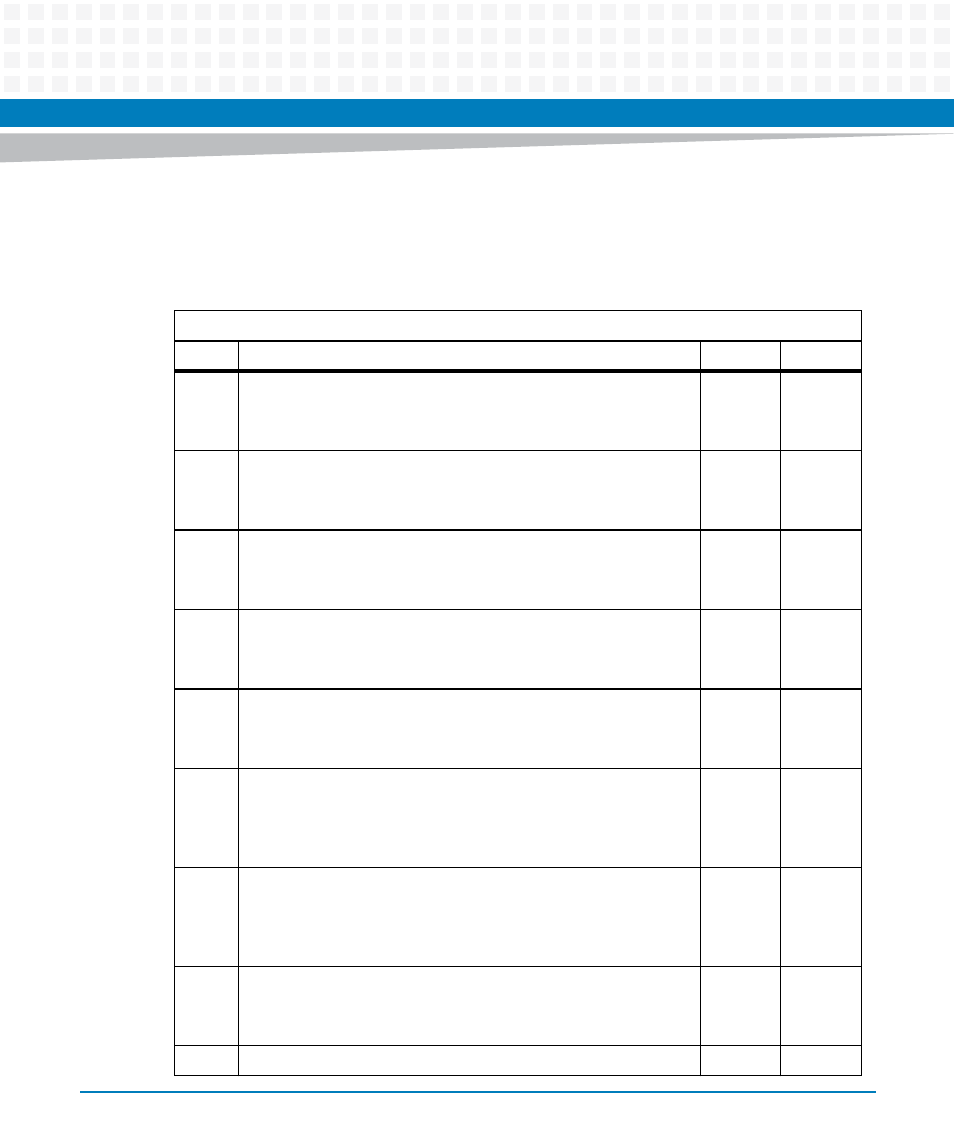

Table 8-139 SPP Interrupt Group Status Registers

Address Offset: 0x90 - 0x91

Bit Description

Default

Access

0

Cascade Group. See 1.1.3.35.1Cascade Interrupt Registers:

0: No Interrupt

1: Interrupt from Cascade Group

0

SPP: r

1

Watchdog Group. See 1.1.3.35.2Watchdog Interrupt Registers:

0: No Interrupt

1: Interrupt from Watchdog Group

0

SPP: r

2

Remote Group. See 1.1.3.35.3Remote Interrupt Registers:

0: No Interrupt

1: Interrupt from Remote Group

0

SPP: r

3

IPMC Group. See 1.1.3.35.4IPMC Interrupt Register:

0: No Interrupt

1: Interrupt from IPMC Group

0

SPP: r

4

ARTM Group. See 1.1.3.35.8ARTM Interrupt Registers:

0: No Interrupt

1: Interrupt from ARTM Group

0

SPP: r

5

Miscellaneous Group. See1.1.3.35.7Miscellaneous Interrupt

Registers:

0: No Interrupt

1: Interrupt from Miscellaneous Group

0

SPP: r

6

Telecom Clock Group. See 1.1.3.35.5Telecom Clocking Interrupt

Registers:

0: No Interrupt

1: Interrupt from Telecom Clock Group

0

SPP: r

7

Failover Group. See 1.1.3.35.6Failover Interrupt Registers:

0: No Interrupt

1: Interrupt from Failover Group

0

SPP: r

15:8

Reserved

0

r