Table 8-30, Lpc i/o register map overview, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 266

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

266

8.2.2.1.2 GPP LPC Decoding

The LPC bus supports different protocols.

LPC I/O Decoding

The LPC interface responds to LPC I/O accesses listed in the

. All other LPC I/O

accesses are ignored.

All LPC I/O accesses to address POSTCODE, within the address range REGISTERS and within the

address ranges of COM1 or COM2 (only when enabled during Super IO configuration) are

decoded by the LPC core.

LPC Memory Decoding

The LPC interface never responds to LPC Memory accesses.

LPC Firmware Decoding

The LPC interface never responds to LPC Firmware accesses.

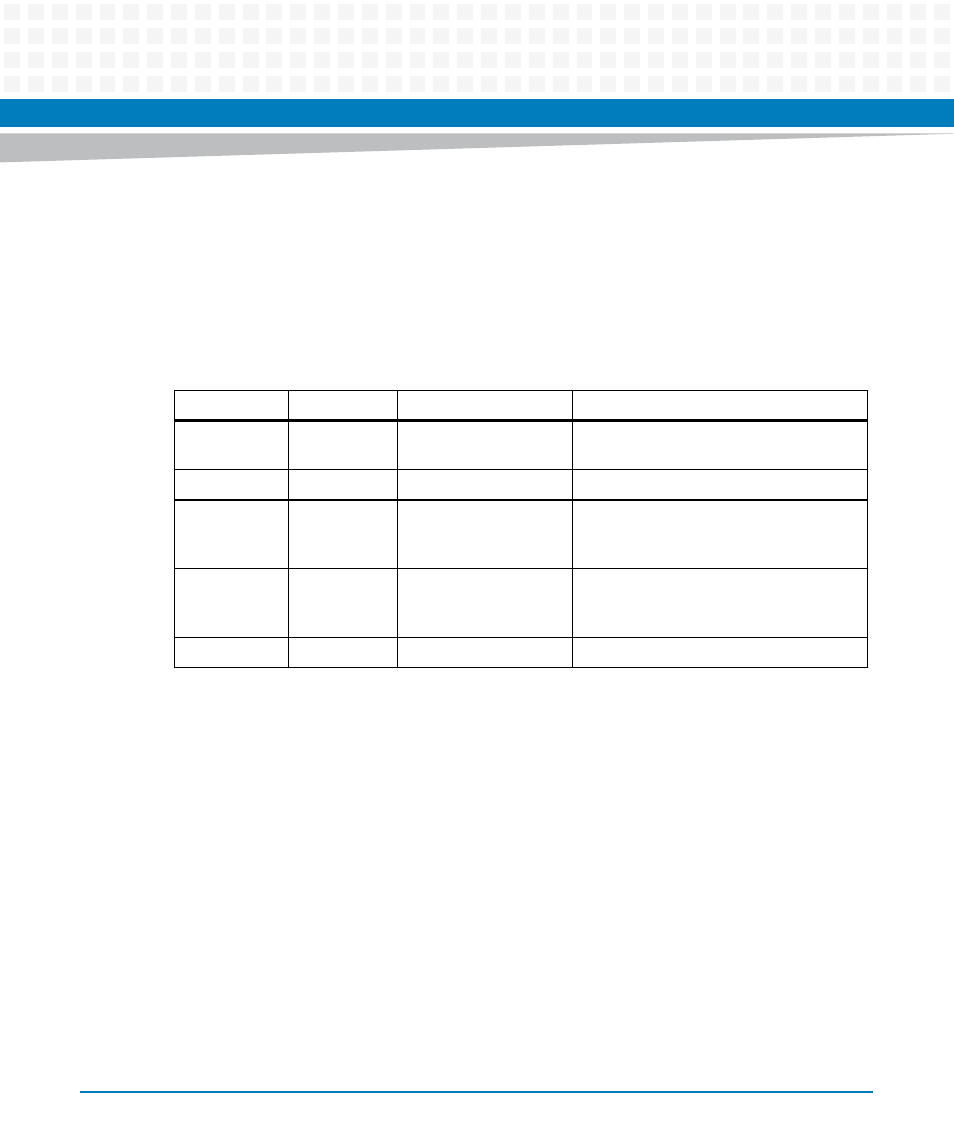

Table 8-30 LPC I/O Register Map Overview

Base Address

Address Size

Address Range Name

Description

0x4E

2

SIW

Super IO Configuration Registers for

Index and Date

0x80

1

POSTCODE

POST Code Register

BASE1

8

COM1

COM1. Serial Port 1 (Logical Device 4).

BASE1 address is set up during Super IO

Configuration.

BASE2

8

COM2

COM2. Serial Port 2. (Logical Device 4).

BASE2 address is set up during Super IO

Configuration.

0x600

128

REGISTERS

Glue Logic FPGA Registers