Table 8-176, Test pattern generator link and timeslot register, Table 8-177 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 387: Test pattern generator data register, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

387

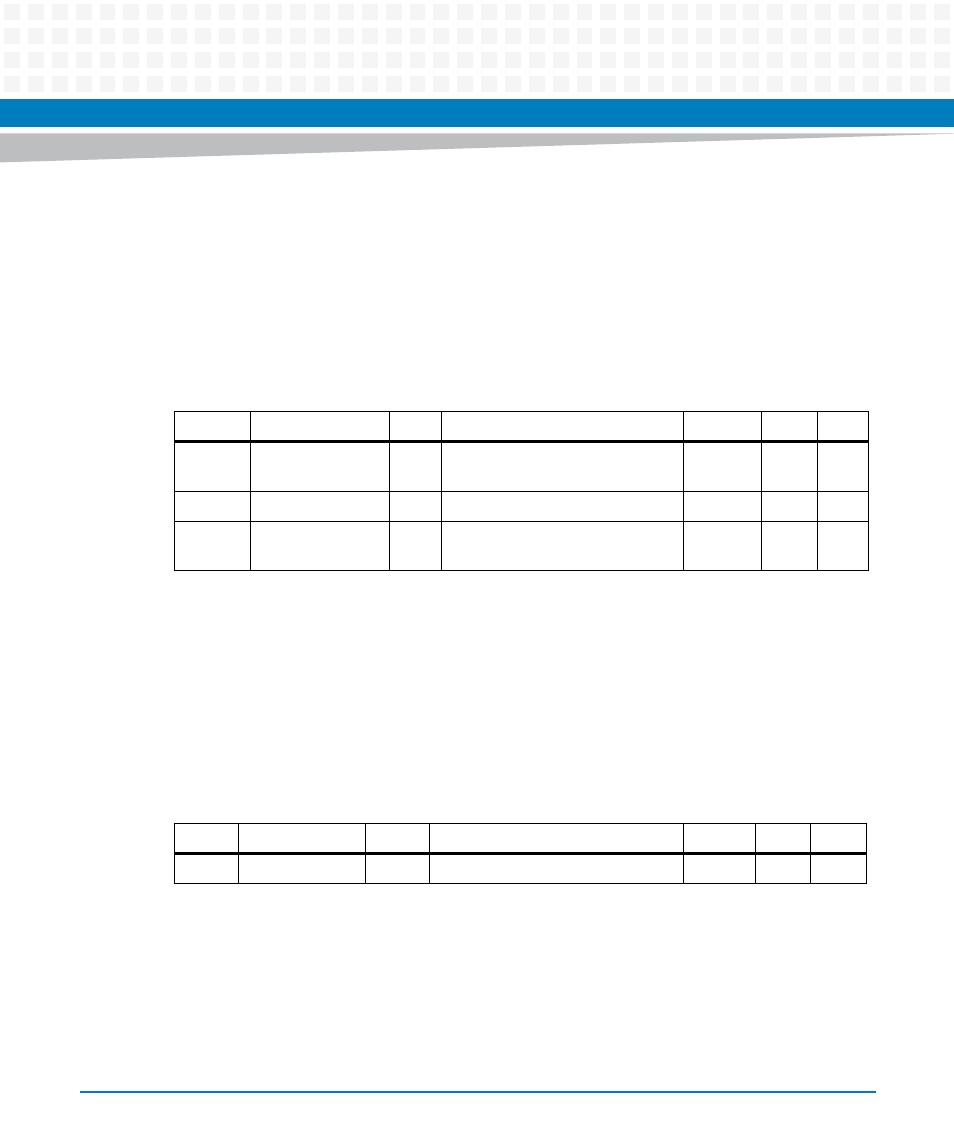

8.4.2.2.1 Test Pattern Generator Link and Timeslot Register

Address: 0x50, TstPatGenLnkTsReg

Width: 16 bit

This registers selects timeslot TSIP-link for the test pattern transmission of instead of payload

data.

8.4.2.2.2 Test Pattern Generator Data Register

Address: 0x52, TstPatGenDatReg

Width: 8 bit

This registers provides the test pattern to be transmitted in the case of static pattern

transmission. Not used in the case of pseudo random pattern transmission.

8.4.2.2.3 Test Pattern Generator Control Register

Address: 0x53, TstPatGenCtrlReg

Width: 8 bit

Table 8-176 Test Pattern Generator Link and Timeslot Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

15...10

TstPatGenLinkNo

RW

Selects the transmit Link 0..59,

(60..63 will be same as 0)

0x0

X

X

9

-

-

reserved

undef

-

-

8...0

TstPatGenTsNo

RW

Selects the transmit timeslot

(0..511)

0x0

X

X

Table 8-177 Test Pattern Generator Data Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...0

TstPatGenData

RW

Static test pattern data

0x0

X

X