Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 380

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

380

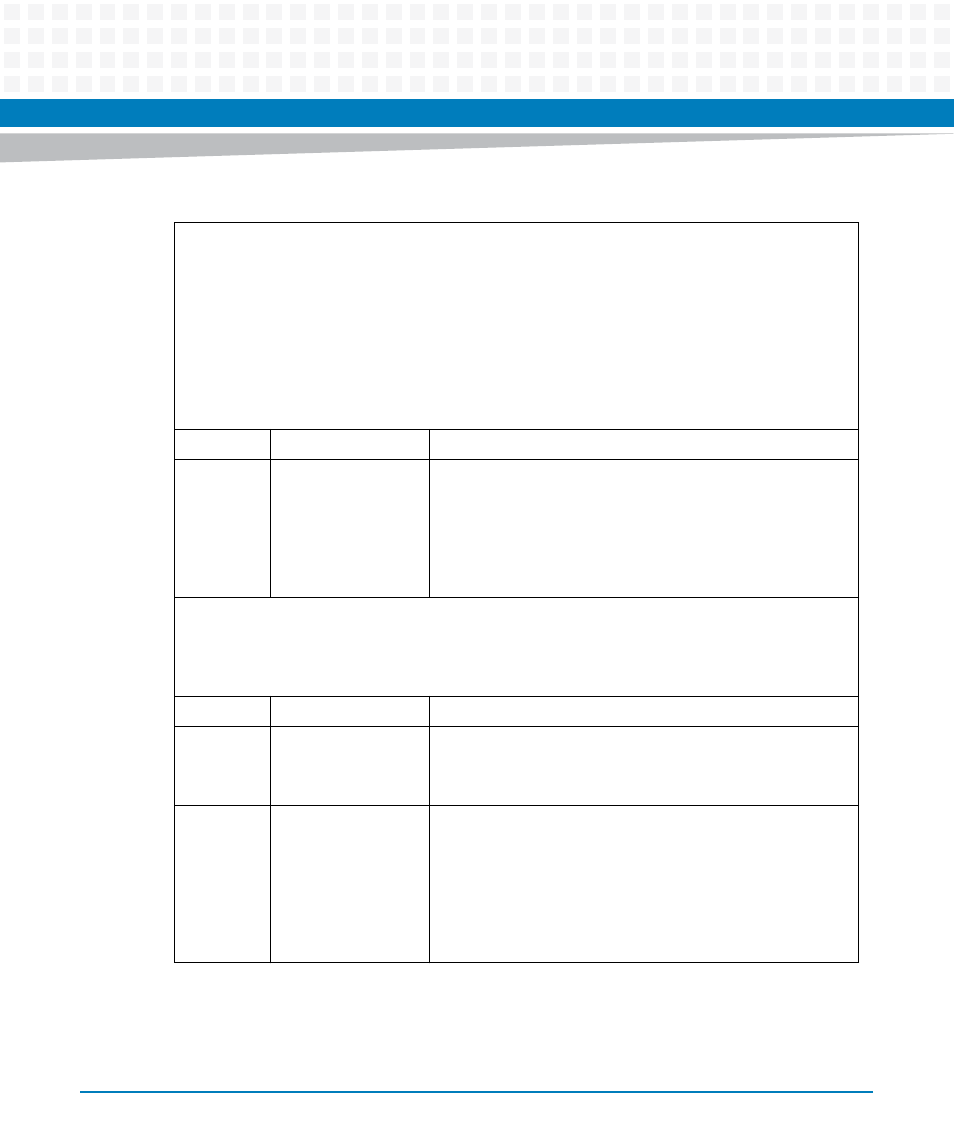

DMC Power Supply Control Block (DmcPwrCtrlBlk) [Hw: Cy0]

This Block performs the power sequencing for the DSP power supply. It contains a monitor register

to indicate the voltage

which has caused a potential power supply failure after the DMC has powered up. If one of the power

supplies fails the DMC

is powered down by the DspFpga and the board is informed by the deactivating the DMC_PWRGD

signal.

Access via SPI- bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block:

B0...BF

Address

Acronym

Description

0xB0

DmcPwrMonReg

DMC Power Supply Monitor Register (8bit) [Hw: syn, WAck1,

RAck1]

This register monitors power supply failures (power loss and

power interrupt) to identify the power supply which has

caused a power down of the DMC.

General Registers (GnrlRegs) [Hw: Cy0]

Collection of general register not dedicated to particular functions

Access via SPI- bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block:

C0...D7

Address

Acronym

Description

0xC0

SoftResReg

Soft Reset Register (32bit) [Hw: syn, WAck1, RAck1, WTP]

Brings by Soft Reset affected registers to power up state

0xC1

SyncErrMonReg

Synchronization and Error Monitor Register (8bit) [Hw: syn,

WAck1, RAck1]

This register monitors the synchronization and error status of

different functions. If a function signals an out of sync or an

error, the respective bit is set. It can be reset by writing the

respective bit in SyncErrMonResReg

Table 8-174 Logic DSP FPGA Register Overview (continued)