Table 8-142, Spp watchdog interrupt status register, Table 8-143 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 336: Spp watchdog interrupt enable register, Table 8-144, Spp remote interrupt status register, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

336

Watchdog Interrupt Registers

Remote Interrupt Registers

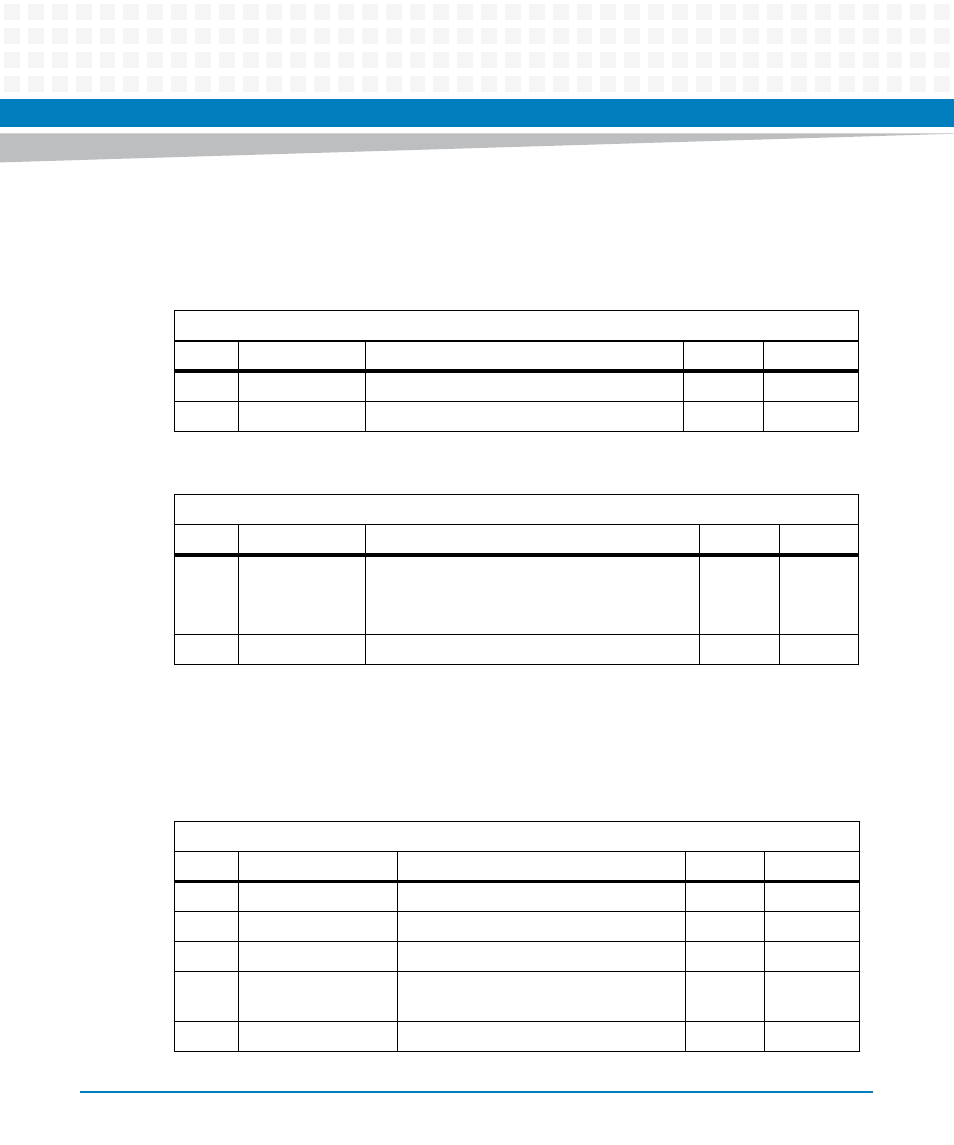

Table 8-142 SPP Watchdog Interrupt Status Register

Address: 0x96 - 0x97

Bit Interrupt

Name

Description

Default

Access

0

WD_HALF

Watchdog half expired

0

SPP: r/w1c

15:1

-

Reserved

0

r

Table 8-143 SPP Watchdog Interrupt Enable Register

Address: 0x98 - 0x99

Bit Interrupt

Name

Description

Default

Access

0

WD_HALF

Watchdog half expired enable.

0: Disabled

1:Enabled

0

SPP: r/w

15:1

-

Reserved

0

r

Table 8-144 SPP Remote Interrupt Status Register

Address: 0x9A - 0x9B

Bit Interrupt

Name

Description

Default

Access

0

REMOTE_RESET_A

GPP Reset

0

SPP: r/w1c

1

REMOTE_RESET_D

GPP Reset deasserted

0

SPP: r/w1c

2

REMOTE_WD_HALF

GPP Watchdog half expired

0

SPP: r/w1c

3

REMOTE_WD_RESE

T

GPP Watchdog expired. GPP watchdog

reset.

0

SPP: r/w1c

7:4

MAILBOX[4:1]

GPP Mailbox 1 to 4 written.

0

SPP: r/w1c