Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 283

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

283

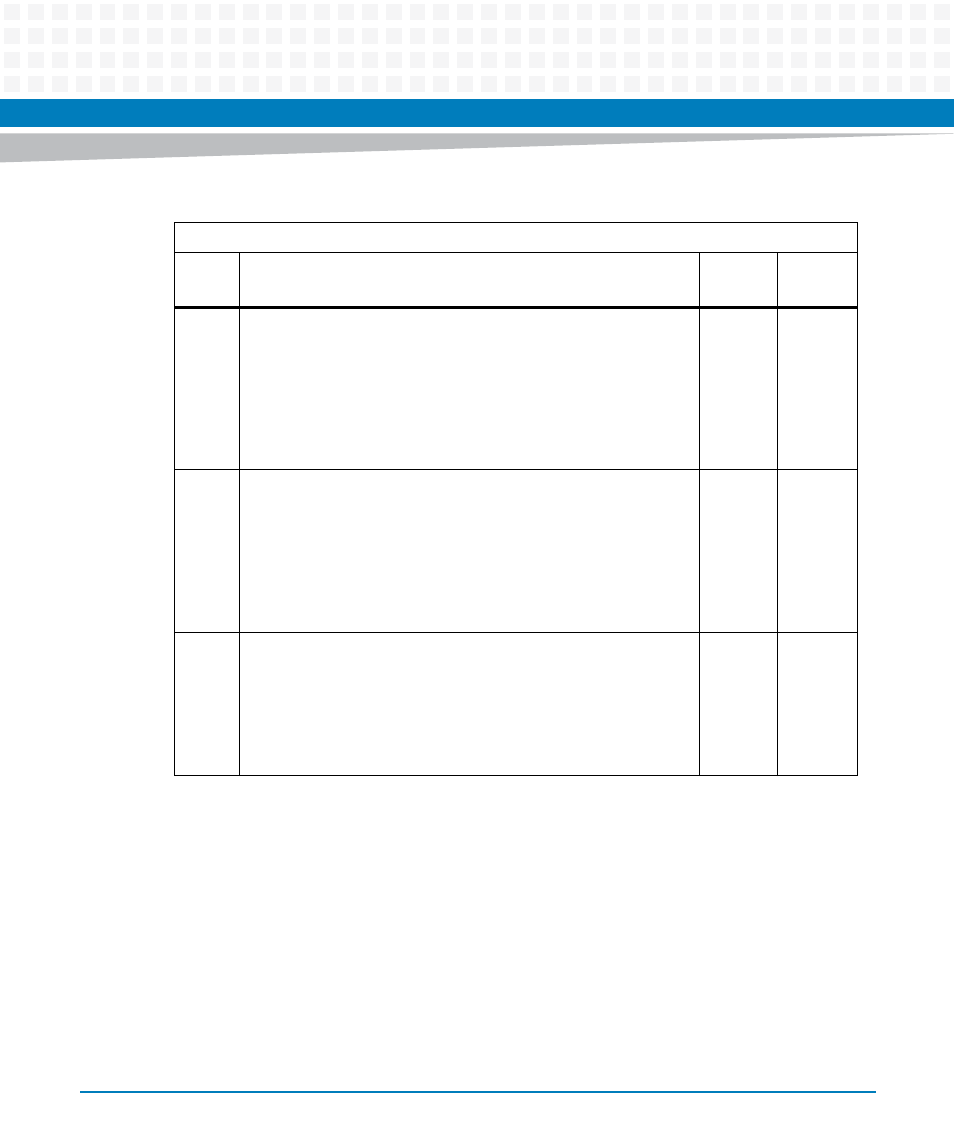

- Modem Control Register (MCR)

5

Stick parity

When bits 3, 4, and 5 are set, the parity bit is transmitted and

checked as cleared. When bits 3 and 5 are set and bit 4 is cleared,

the parity bit is transmitted and checked as set. If bit 5 is cleared,

stick parity is disabled.:

1: Stick parity enabled

0: Stick parity disabled

0

GPP: r/w

6

Break control bit

Bit 6 is set to force a break condition, i.e. a condition where TXD is

forced to the spacing (cleared) state. When bit 6 is cleared, the

break condition is disabled and has no affect on the transmitter

logic. It only effects TXD:

1: Break condition enabled

0: Break condition disabled

0

GPP: r/w

7

Divisor latch access bit (DLAB)

Bit 7 must be set to access the divisor latches of the baud

generator during a read or write. Bit 7 must be cleared during a

read or write to access the RBR, THR, or IER.:

1: Access to DLL and DLM registers

0: Access to RBR, THR and IER registers

0

GPP: r/w

Table 8-57 Line Control Register (LCR) (continued)

IO Address: Base + 3

Bit

Description

Default

Access