Table 8-110, Telecom clock enable/control register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 319: 25 telecom clocking registers

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

319

8.2.2.3.25 Telecom Clocking Registers

Telecom Clock Control Registers

The Telecom Clock Enable Register controls the output enable signals and the signal source for

the telecom clocking chassis #1. Reset has no effect to the register contents.

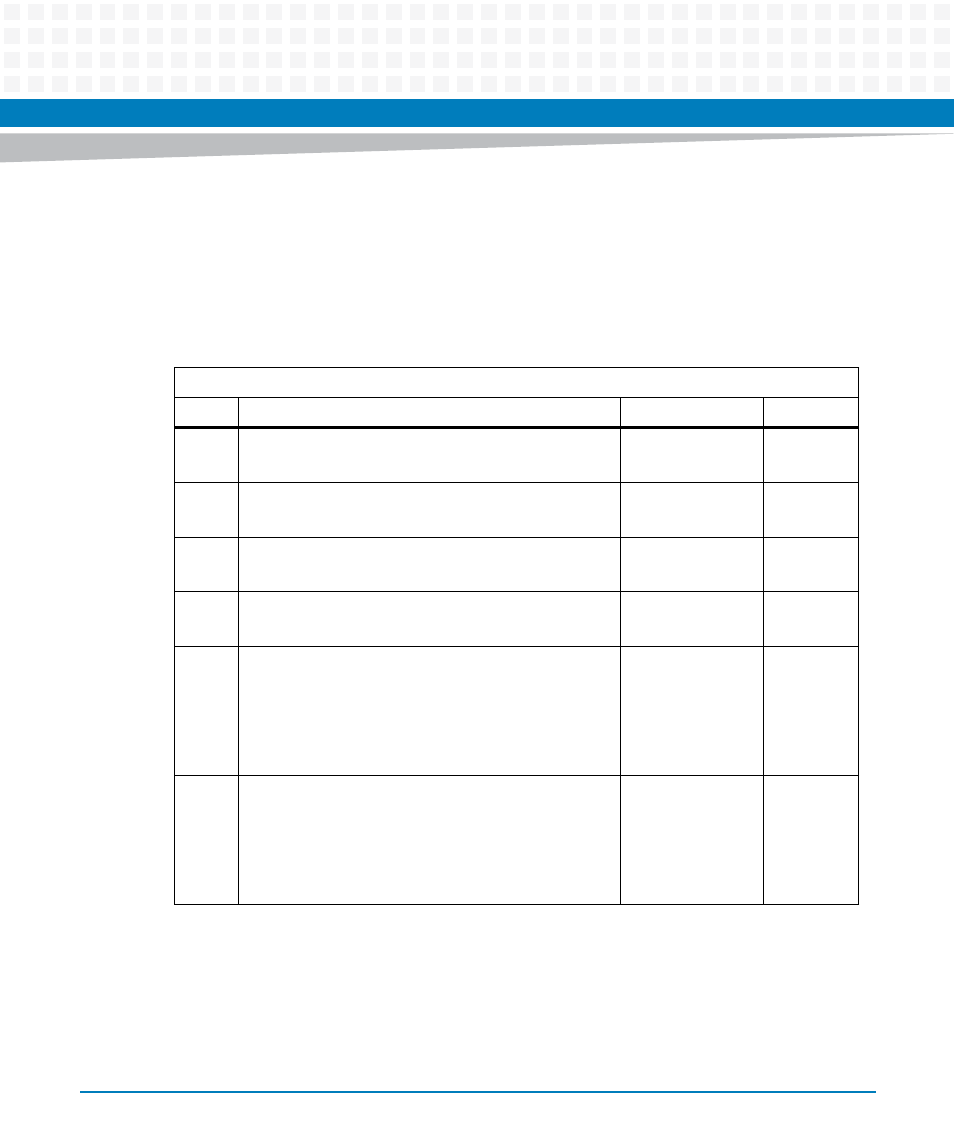

Table 8-110 Telecom Clock Enable/Control Register

Address: 0x60

Bit

Description

Default

Access

0

0: Drive EN_CLK2A low, CLK2A is disabled

1: Drive EN_CLK2A high, CLK2A is enabled

PWR_GOOD: 0

SPP: r/w

1

0: Drive EN_CLK2B low, CLK2B is disabled

1: Drive EN_CLK2B high, CLK2B is enabled

PWR_GOOD: 0

SPP: r/w

2

0: Drive EN_CLK3A low, CLK3A is disabled

1: Drive EN_CLK3A high, CLK3A is enabled

PWR_GOOD: 0

SPP: r/w

3

0: Drive EN_CLK3B low, CLK3B is disabled

1: Drive EN_CLK3B high, CLK3B is enabled

PWR_GOOD: 0

SPP: r/w

5:4

MSSYNC Select:

0: Off. Drive low

1: Clock CLK2A is selected

2: Clock CLK2B is selected

3: Reserved

PWR_GOOD: 0

SPP: r/w

7:6

SYNC2K Select:

0: Frame Sync Clock CLK_FRSYNC_IN

1: Clock CLK2A is selected

2: Clock CLK2B is selected

3: Reserved

PWR_GOOD: 0

SPP: r/w