2 cpld registers detailed description, Table 8-4, Cpld code version register – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 248: Cpld, Registers detailed description, Cpld and fpga, 1 cpld code version register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

248

8.1.2.2

CPLD Registers Detailed Description

8.1.2.2.1 CPLD Code Version Register

0x08

SPI: r

Power-Up Failure Codes Part 1 Register

0x09

SPI: r

Power-Up Failure Codes Part 2 Register

0x0A

SPI: r

Power-Up Failure Codes Part 3 Register

0x0B

SPI: r

Power-Up Failure Codes Part 4 Register

0x0C

SPI: r

Power-Up Failure Codes Part 5 Register

0x0D

SPI: r

Power-Up Failure Codes Part 6 Register

0x0E

SPI: r/w

Test Register

0xF

r

Reserved

0x10

SPI: w

Glue FPGA force golden image or reload image Register

0x11

w

DMC Base FPGA force golden image or reload image Register

0x12

w

DMC 1 FPGA force golden image or reload image Register

0x13

w

DMC 2 FPGA force golden image or reload image Register

0x14

w

RTM FPGA device 0 force golden image or reload image Register

0x15

w

RTM FPGA device 1 force golden image or reload image Register

0x16

w

RTM FPGA device 2 force golden image or reload image Register

0x17 - 0x1F

r

Reserved

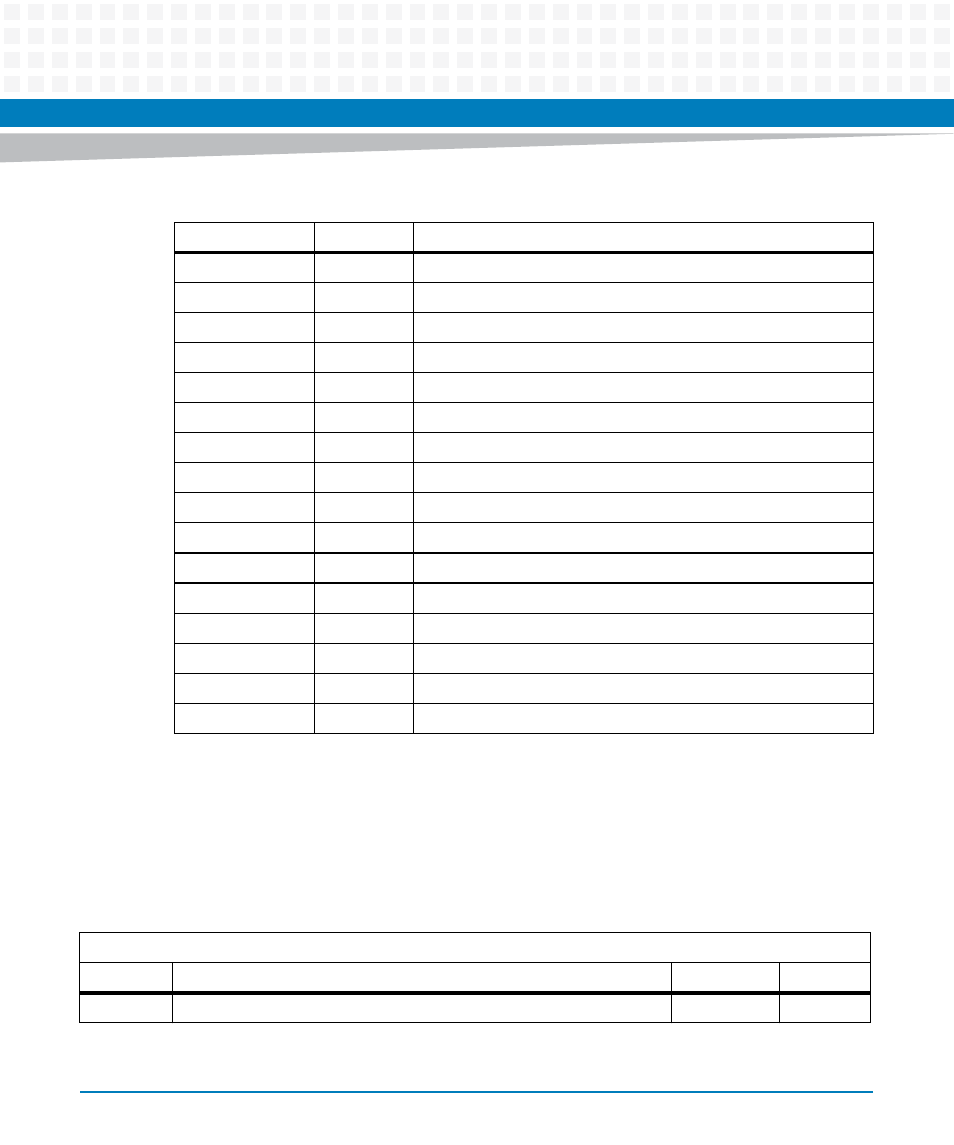

Table 8-3 CPLD Register Overview (continued)

CPLD Address

Type

Description

Table 8-4 CPLD Code Version Register

CPLD Address: 0x00

Bit Description

Default

Access

7:0

CPLD Version. Incremented with each new version.

0x1

r