U-boot – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 192

U-Boot

ATCA-8310 Installation and Use (6806800M72E)

192

The TSI572 routing table is set up so that:

Accesses coming in via the P4080 SRIO interface #1 are forwarded to ports 6, 2 and 4 (start

of DSP chain)

Accesses coming in via the P4080 SRIO interface #2 are forwarded to ports 7, 3 and 5 (end

of DSP chain).

This ensures that even for the case that a DSP chain is broken; DSPs that would be inaccessible

via one chain are still accessible via the 2nd chain.

There are two 128MB address ranges reserved in the P4080 address space, one for SRIO

interface 1 at address 0xd0000000, one for SRIO interface 2 at address 0xe0000000.

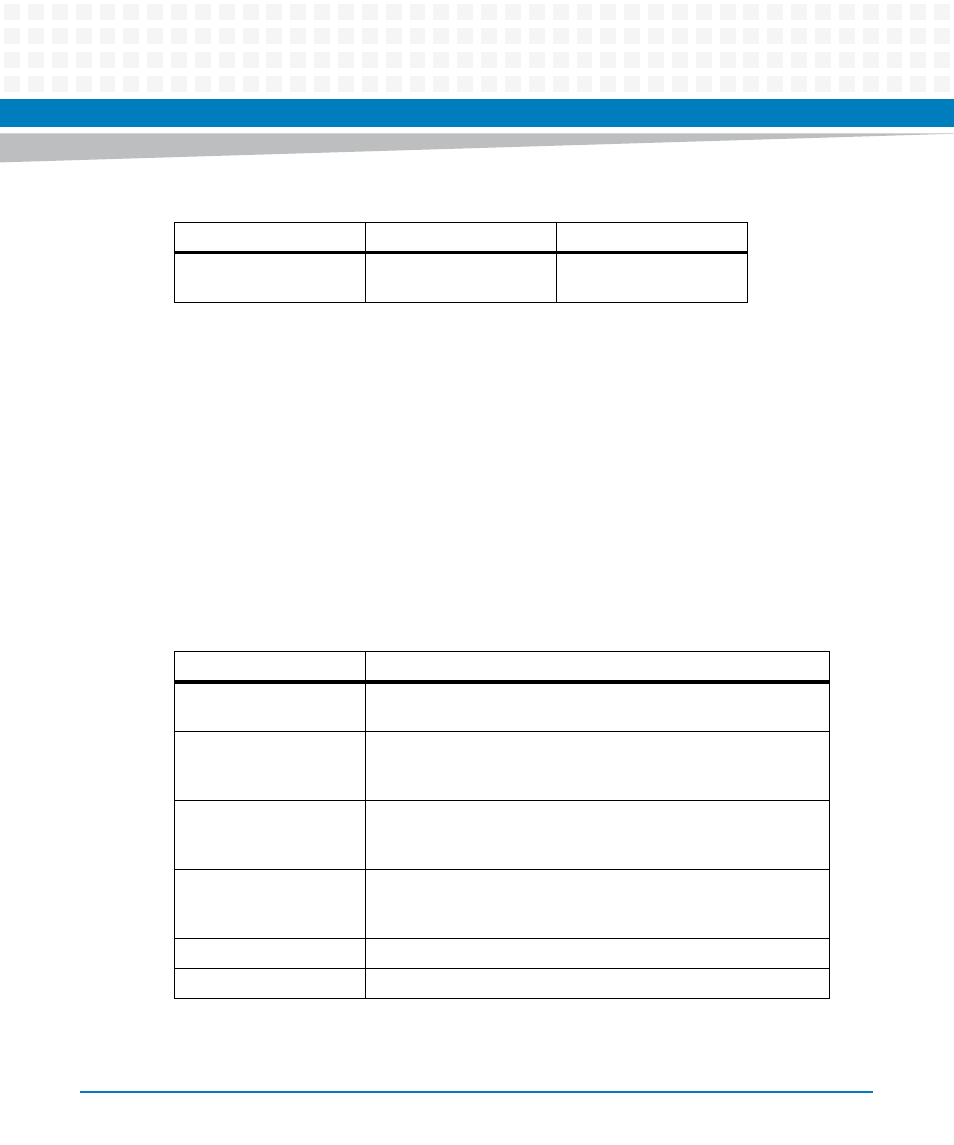

Each 128MB window is further split into sub-segments according to the following table:

DMC2 DSPs

0x30 .. 0x39

4 (start of chain)

5 (end of chain)

Address Range Offset

Usage

0x0000000 .. 0x8000000

Window for NREAD/NWRITE accesses. Can be used to access DSP

memory ranges.

0x8000000 .. 0x9000000

Maintenance accesses to onboard. Each DSP has a 1MB address

range within this address window (DSP1 at offset 0, DSP1 at offset

0x100000, …)

0x9000000 .. 0xa000000

Maintenance accesses to DMC1 DSPs. Each DSP has a 1MB address

range within this address window (DSP1 at offset 0, DSP1 at offset

0x100000, …)

0xa000000 .. 0xb000000

Maintenance accesses to DMC2 DSPs. Each DSP has a 1MB address

range within this address window (DSP1 at offset 0, DSP1 at offset

0x100000, …)

0xb000000 .. 0xb100000

Maintenance access to TSI572

0xb100000 .. 0xb200000

Used for enumeration

Table 6-9 Port and SRIO Target ID Assignment (continued)

Device

Target ID(s)

TSI572 Port(s)