Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 376

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

376

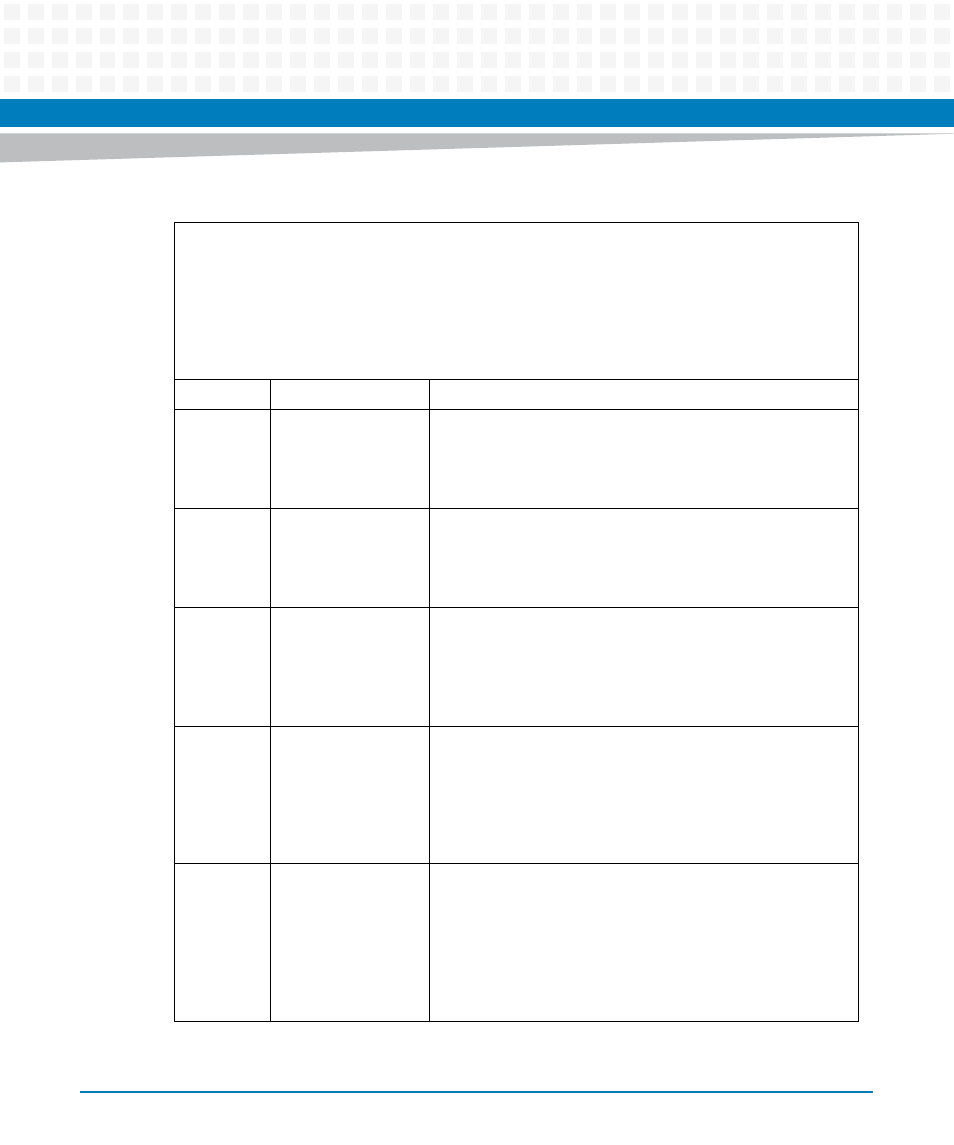

Deserializer to TSIP Allocater Block (Des2TsipBlk) [Hw: Cy0]

The Des2TsipBlk allocates data from the 16 bit parallel interface of the SerDes IP block to 60 TSIP-

links.The received supplemental channel test pattern data can be read by using the registers of this

block. Furthermore the CRC status signals from the SerDes IP Block are evaluated and CRC errors are

counted and indicated.

Access via SPI- bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block:

80...97

Address

Acronym

Description

0x80

SerDesRcvCtrlReg

Serdes Receiver Control Register (8bit) [Hw: syn, WAck1,

RAck1]

A Serdes reset or resync can be initiated via this register

0x81

SerDesRcvStatReg

Serdes Receiver Status Register (8bit ) [Hw: syn, WAck1,

RAck1]

The Serdes receiver status is shown

0x82

SupplTstPatDataRcv

DatReg

Supplemental Test Pattern Receive Data Register (16bit ) [Hw:

asyn, WAck2, RAck2]

This register provides the received test pattern from the

supplementary channel

0x84

SupplTstPatDataCm

pDatReg

Supplemental Test Pattern Compare Data Register (16bit)

[Hw: asyn , WAck2 , RAck2]

This register determines the data the received test pattern

from the supplementary channel are compared to for error

counting

0x86

TstPatErrCntCtrlReg

Test Pattern, CRC and Disparity Error Counter Control Register

(8bit ) [Hw: asyn, WAck2, RAck2]

This register controls the error counter of static test pattern

received via the supplementary channel, it controls the error

counter for CRC error rate evaluation and the counter totally

transferred frame counter.

Table 8-174 Logic DSP FPGA Register Overview (continued)