Cpld and fpga, 6 test frame count register – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 400

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

400

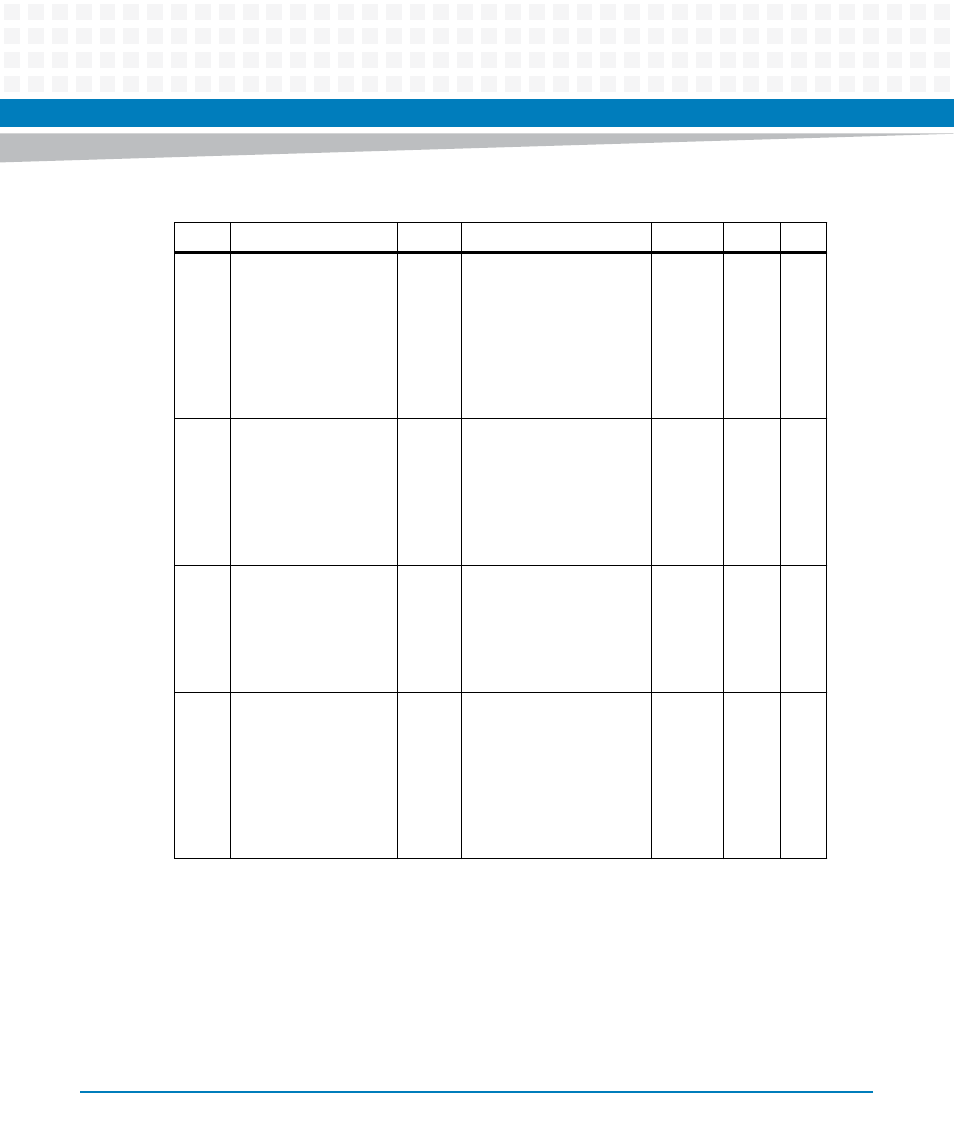

8.4.2.5.6 Test Frame Count Register

Address: 0x88, TstFrameCntReg

Width: 32 bit

3

FrameCntRun

RW

0x1: FrameCntRun, starts

frame counting for test

pattern and CRC error

rate evaluation.

Des2TsipFrameCntReg is

cleared by changing the

value of this bit from 0 to

1.

0b0

X

X

2

DispErrCntRun

RW

0x1: DispErrCntRun,

starts Disparity error

counting.

Des2TsipDispErrCntReg is

cleared by changing the

value of this bit from 0 to

1.

0b0

X

X

1

CrcErrCntRun

RW

0x1: CrcErrCntRun, starts

CRC error counting.

Des2TsipCrcErrCntReg is

cleared by changing the

value of this bit from 0 to

1.

0b0

X

X

0

SupplTstPatErrCntRun RW

0x1:

SupplTstPatErrCntRun,

starts pattern error

counting.

Des2TsipSupplTstPatErrC

ntReg is cleared by

changing the value of this

bit from 0 to 1.

0b0

X

X

Table 8-193 Test Pattern, CRC and Disparity Error Counter Control Register (continued)

Bit

Acronym

Type

Description

Default

Pwr

Soft