Table 8-91, Real time clock register, Table 8-92 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 311: Real time clock latch register, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

311

8.2.2.3.17 Real Time Clock Registers

The Real Time Clock is a 32 bit counter which is incremented every second. The SPP can load a

start value and restart the counter.

A write access to the Real Time Clock Latch Register latches the current 32 bit counter value.

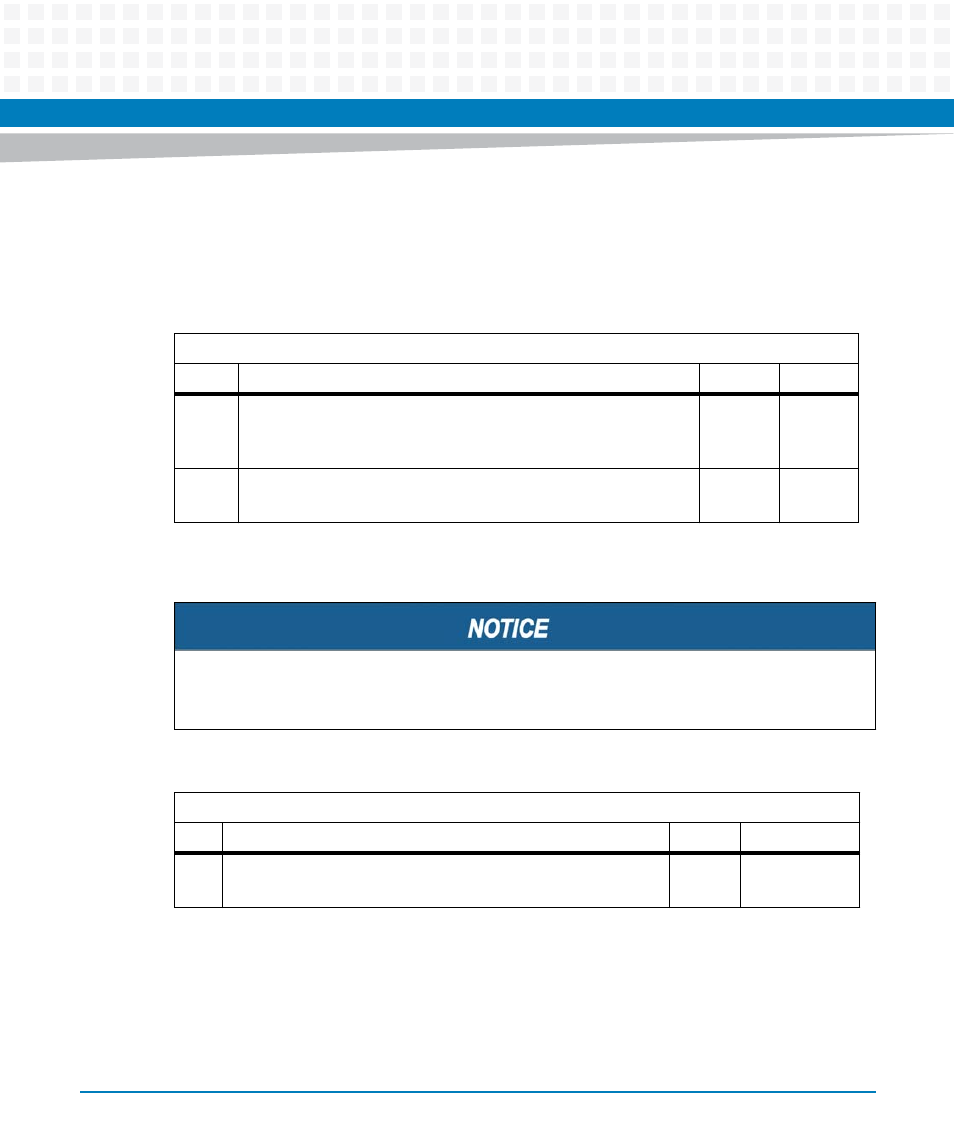

Table 8-91 Real Time Clock Register

Address: 0x01C - 0x1F

Bit Description

Default

Access

31:0

32 Bit Counter. Incremented every second.

When loaded the counter restarts when the bits [31:24] are

written.

0

SPP: w

Latched 32 Bit Real Time Clock counter value.

0

SPP: r

GPP: r

Only when 0x1xF is written the Real Time Clock is loaded with the values previous written to

the addresses 0x1C to 0x1E and the value of write data of 0x01F.

Table 8-92 Real Time Clock Latch Register

Address: 0x01C

Bit Description

Default

Access

7:0

Real Time Clock Latch.

Latch current Real Time Clock content.

-

SPP: w GPP: w