Table 8-56, Fifo control register (fcr), Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 281

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

281

FCR is a write-only register that is located at the same address as the IIR (IIR is a read-only

register). FCR enables/disables the transmitter/receiver FIFOs, clears the transmitter/receiver

FIFOs, and sets the receiver FIFO trigger level.

- Line Control Register (LCR)

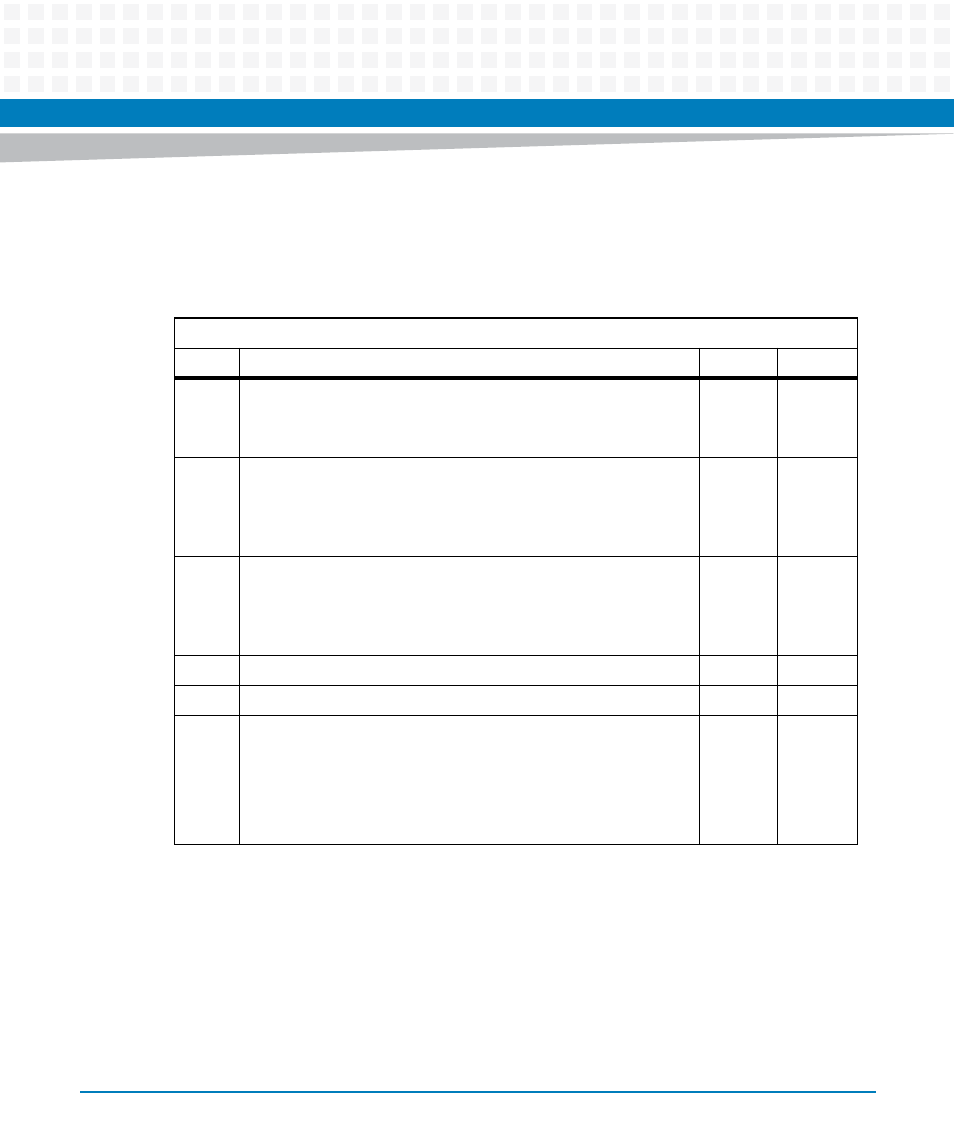

Table 8-56 FIFO Control Register (FCR)

IO Address: Base + 2

Bit Description

Default

Access

0

FIFO enable/disable:

1: Transmitter and Receiver FIFO enabled

0: FIFO disabled

0

GPP: w

1

Receiver FIFO reset:

1: Bytes in receiver FIFO and counter are reset. Shift register is not

reset (bit is self-clearing)

0: No effect

0

GPP: w

2

Transmit FIFO reset:

1: Bytes in receiver FIFO and counter are reset. Shift register is not

reset (bit is self-clearing)

0: No effect

0

GPP: w

3

Receiver/Transmitter ready. Not supported.

0

GPP: w

5:4

Reserved

0

GPP: w

7:6

Receiver FIFO interrupt trigger level:

00: 1 byte

01: 4 bytes

10: 8 bytes

11: 14 bytes

0

GPP: w