Figure 7-1, Ipmc/mmc block diagram of the atca-8310, Intelligent peripheral management controller – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 203

Intelligent Peripheral Management Controller

ATCA-8310 Installation and Use (6806800M72E)

203

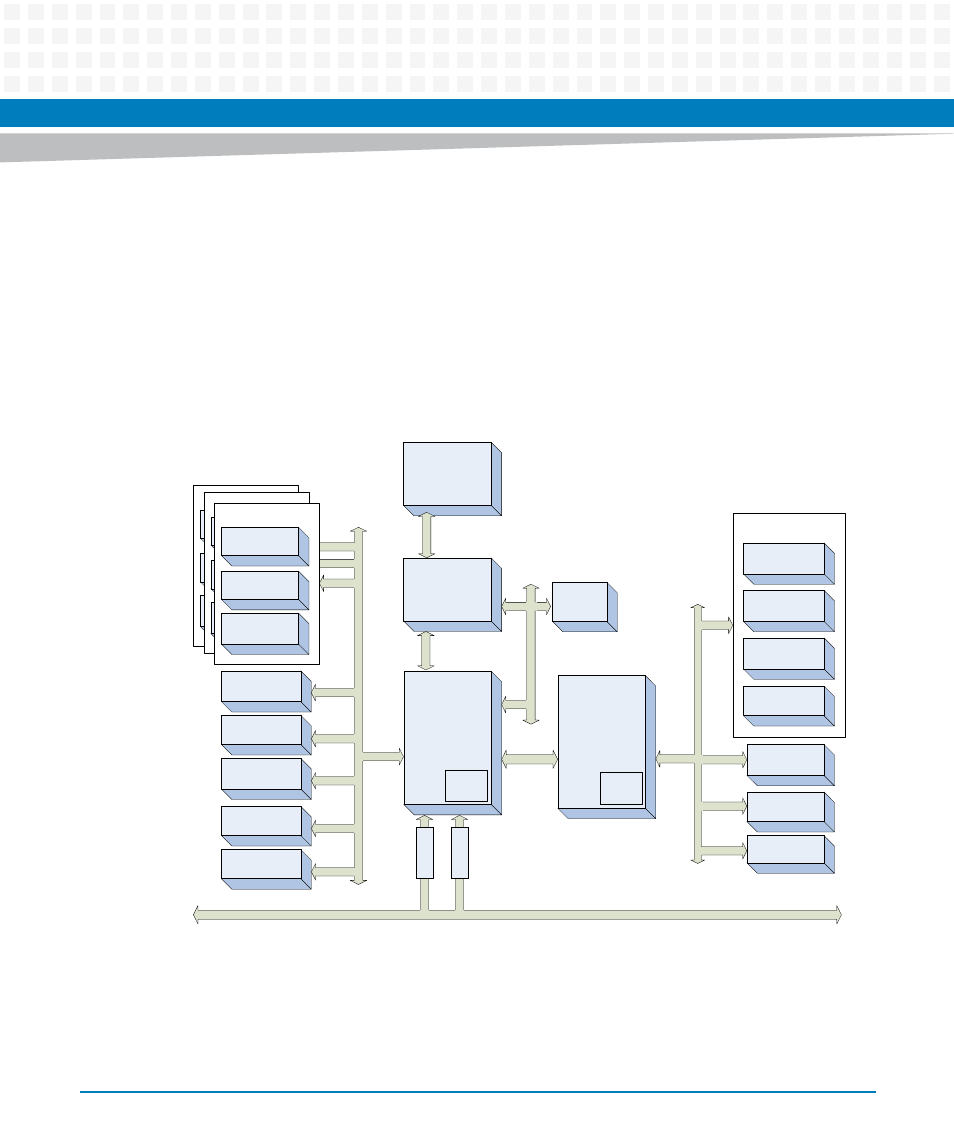

Registers within the Glue Logic FPGA and the Power CPLD can be accessed by the IPMC via SPI

bus. This enhances the capabilities of the IPMC. The Glue Logic FPGA can be used to monitor

the CPU status, the Payload reset cause, the port80 BIOS post codes and to control the boot

bank selection of the Intel CPU. The Power CPLD controls the enabling and monitoring of power

good signals from all on-board power converters.

A functional block diagram of the ATCA-8310 IPMC/MMC system is shown in the following

figure:

Figure 7-1

IPMC/MMC block diagram of the ATCA-8310

FRU Information

Temperature

Sensor

Presence Sensor

DSP Module

FRU Information

Temperature

Sensor

Presence Sensor

DMC Module

Renesas H8S

2166 (IPMC)

I

2

C

IPMB-0

IP

MB

-A

IP

MB

-B

IPMB-L

ATMEGA 128

(MMC at RTM)

Temperature

Sensors

ATCA-8310 FRU

Information

Power Interface

Sensors

Voltage Sensors

System Event Log

(SEL)

I

2

C

FRU Information

Temperature Sensor

SFP Presence

Sensors

Presence Sensor

Temperature

Sensors

ATCA-8310 FRU

Information

Voltage Sensors

Glue Logic FPGA

KC

S

P4080

Local Bus

FRU Information

Temperature

Sensor

Presence Sensor

DMC Module

Mezzanine Card

WDT

WDT

b

u

f

f

e

r

b

u

f

f

e

r

Power

CPLD

SP

I