Table 8-191, Supplemental test pattern receive data register, Table 8-192 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 399: Supplemental test pattern compare data register, Table 8-193, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

399

Width: 16 bit

This register provides the received test pattern from the supplementary channel.

8.4.2.5.4 Supplemental Test Pattern Compare Data Register

Address:

0x84, SupplTstPatDataCmpDatReg

Width: 16 bit

This register determines the data the received test pattern from the supplementary channel

are compared to for error counting.

8.4.2.5.5 Test Pattern, CRC and Disparity Error Counter Control Register

Address: 0x86, TstPatErrCntCtrlReg

Width: 8 bit

This register controls the error counter of static test pattern received via the supplementary

channel, it controls the error counter for CRC error rate evaluation and the counter totally

transferred frame counter.

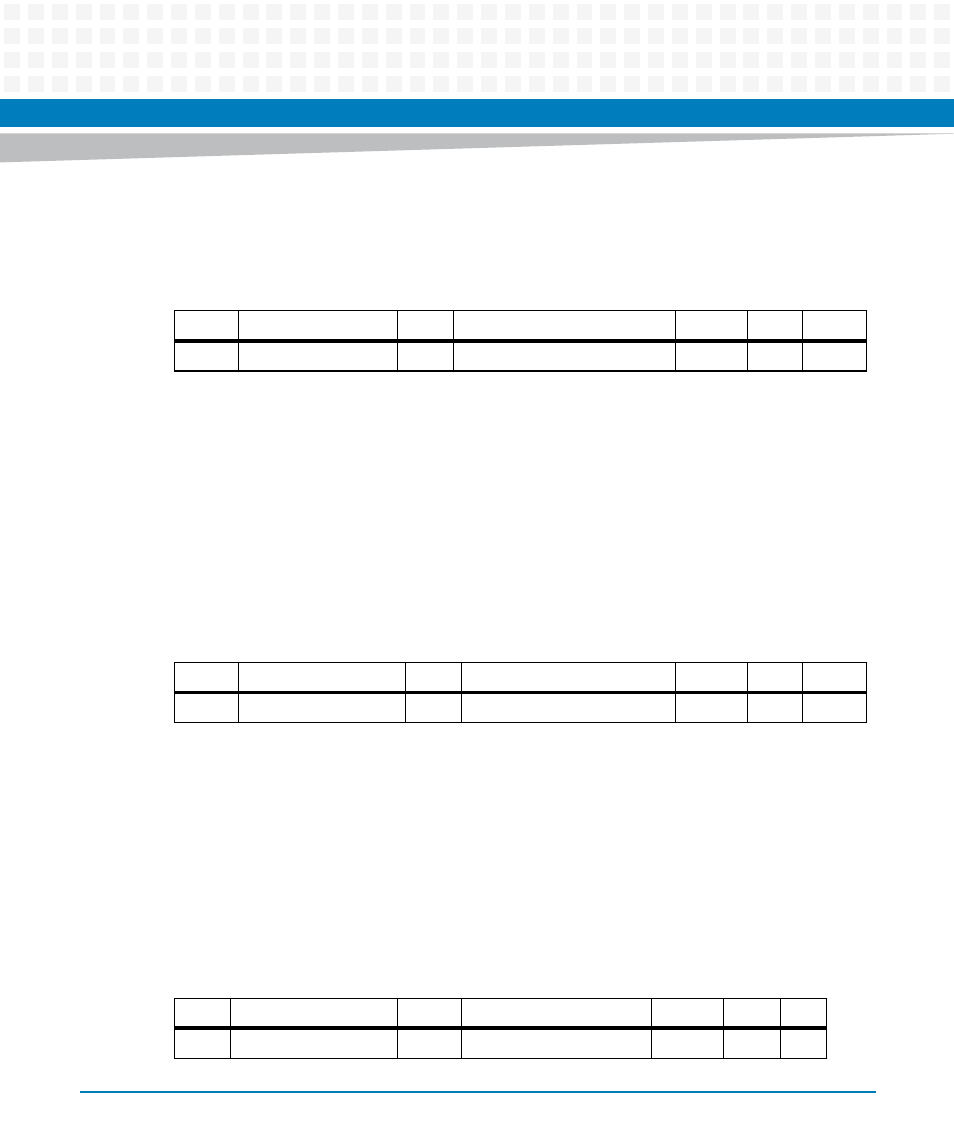

Table 8-191 Supplemental Test Pattern Receive Data Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

15...0

SupplTstPatRcvData

R

Received pattern data.

undef

-

-

Table 8-192 Supplemental Test Pattern Compare Data Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

15...0

SupplTstPatCmpData

RW

compare pattern data.

0x0

X

X

Table 8-193 Test Pattern, CRC and Disparity Error Counter Control Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...4

-

-

reserved

undef

-

-