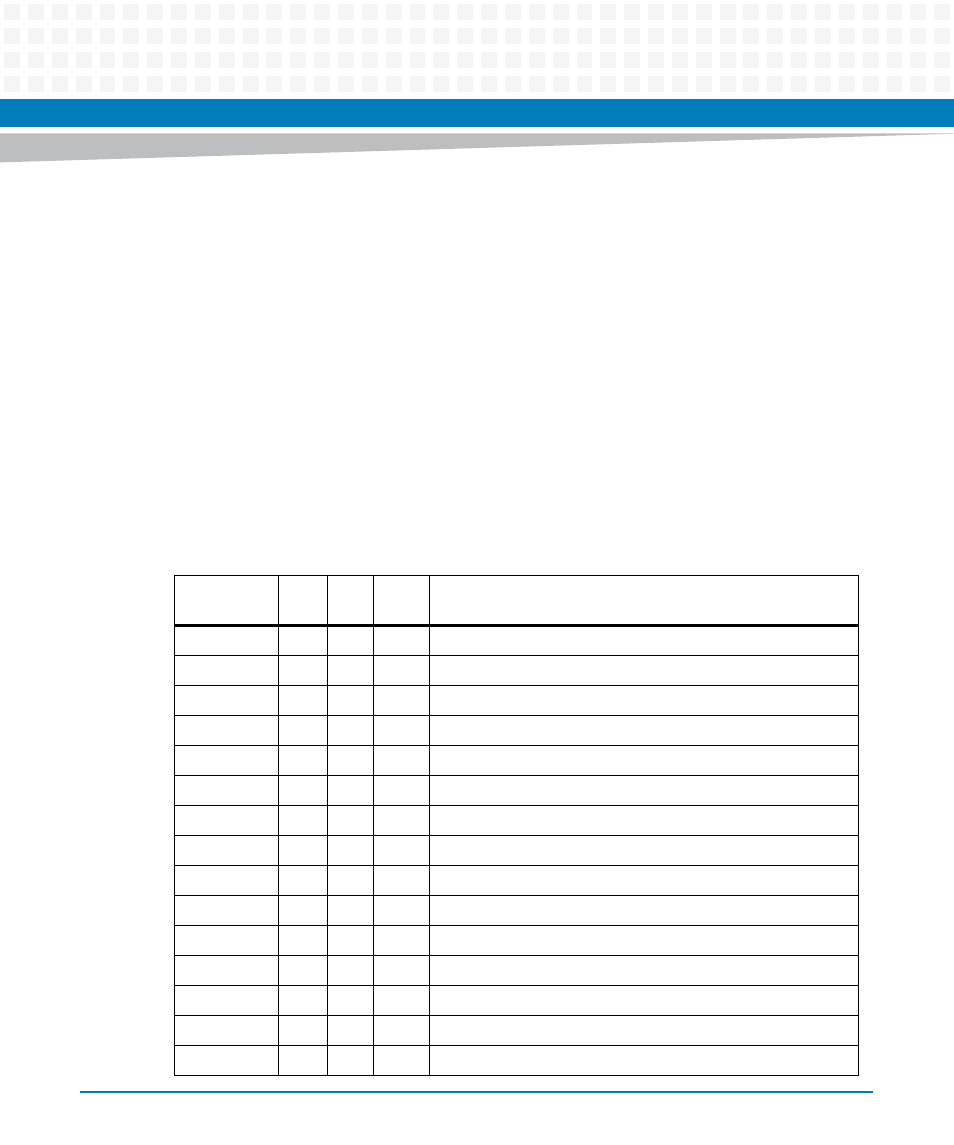

3 glue logic fpga register overview, Table 8-64, Glue fpga register overview – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 292: Table "glue fpga register overview" on, Cpld and fpga, 3 ipmc spi register map

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

292

8.2.2.2.3 IPMC SPI Register Map

The FPGA registers may be accessed via IPMC SPI transactions (with the signal

IPMC_SPI_SS_FPGA_ asserted). See

Table "Glue FPGA Register Overview" on page 292

. A SPI

write access to an address not listed in this table or not marked with an "X" in the IPMC SPI

column is ignored. A corresponding read access delivers always zero.

8.2.2.3

Glue Logic FPGA Register Overview

All addresses not listed in the

are reserved. A write to one of these addresses is

ignored.

The SPP uses the Local Bus interface to access the Glue Logic FPGA registers. The GPP uses the

LPC bus to access the Glue Logic FPGA registers. Base IO Address is 0x600. The IPMC uses the

IPMC SPI interface and the corresponding FPGA chip select signal.

Table 8-64 Glue FPGA Register Overview

Address /

Range

SPP

GPP

IPMC

Description

0x00 - 0x01

x

x

x

Glue Logic FPGA Module Identification

0x02 - 0x03

x

x

x

Glue Logic FPGA Code Version

0x04

x

x

x

Serial Line Routing Register

0x05

x

x

x

User LED Control Register

0x06 - 0x07

x

x

x

Status Register

0x08

x

x

x

SPP Boot Bank Selection

0x09

x

x

x

GPP Boot Bank Selection

0x0A - 0x0B

x

x

CPLD SPI Access Registers

0x0C

x

x

SPP BIOS Reset Source Indication Register

0x0D

x

x

BIOS IPMC Watchdog Timeout Register

0x0E

x

x

SPP OS Reset Source Indication Register

0x0F

x

x

OS IPMC Watchdog Timeout Register

0x10

x

x

IPMC Reset Source Indication Register

0x11

x

x

IPMC Watchdog Timeout Register

0x12 - 0x17

x

x

x

Reset Control Registers