12 srio initialization, Table 6-9, Port and srio target id assignment – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 191: U-boot

U-Boot

ATCA-8310 Installation and Use (6806800M72E)

191

setenv hwconfig "fsl_ddr:ctlr_intlv=bank"

Superbank interleaving

setenv hwconfig "fsl_ddr:ctlr_intlv=superbank"

"Disable bank (chip-select) interleaving

setenv hwconfig "fsl_ddr:bank_intlv=null"

Bank (chip-select) interleaving cs0+cs1

setenv hwconfig "fsl_ddr:bank_intlv=cs0_cs1"

Bank (chip-select) interleaving cs2+cs3

setenv hwconfig "fsl_ddr:bank_intlv=cs2_cs3"

"Bank (chip-select) interleaving (cs0+cs1) and (cs2+cs3) (2x2)

setenv hwconfig "fsl_ddr:bank_intlv=cs0_cs1_and_cs2_cs3"

Bank (chip-select) interleaving (cs0+cs1+cs2+cs3) (4x1)

setenv hwconfig "fsl_ddr:bank_intlv=cs0_cs1_cs2_cs3"

Use the "saveenv" command to apply the changes.

6.2.1.12 SRIO Initialization

U-boot sets up the two SRIO interfaces connected to the TSI572 SRIO switch as well as the

TSI572 device itself.

The SRIO switch has two connections to the P4080, and two connections for each of the three

DSP blocks. All DSPs in each DSP block are connected in a daisy chain, with the first and the last

DSP in each chain connected to the SRIO switch.

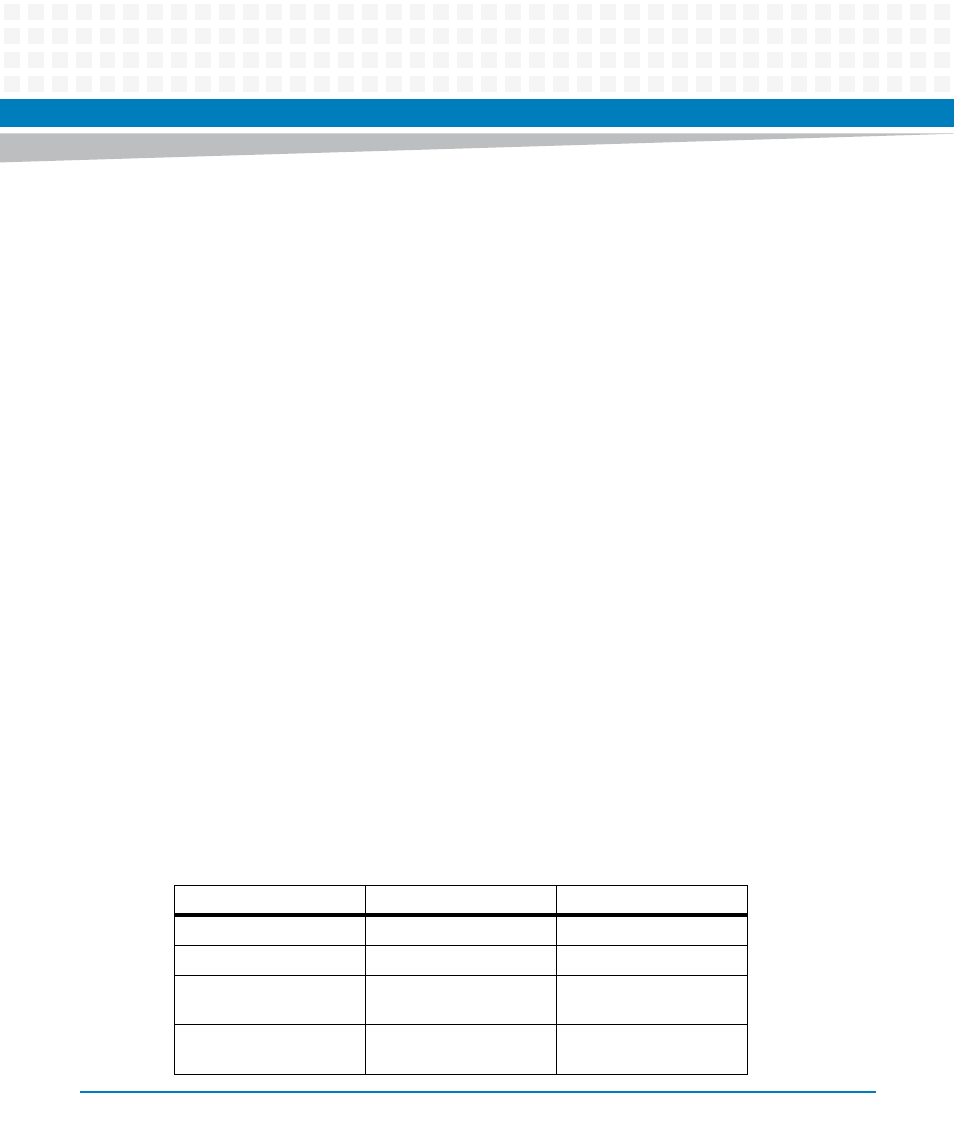

The port and SRIO target ID assignment are shown in the following table:

Table 6-9 Port and SRIO Target ID Assignment

Device

Target ID(s)

TSI572 Port(s)

P4080/SRIO1

0

1

P4080/SRIO2

0x40

0

Onboard DSPs

0x10 .. 0x19

6 (start of chain)

7 (end of chain)

DMC1 DSPs

0x20 .. 0x29

2 (start of chain)

3 (end of chain)