Table 8-179, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 389

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

389

8.4.2.3

TSIP Interface Test Pattern Comparator Block ( TstPatCmpBlk)

Resets:

Pwr = Power On Reset

Soft = Soft Reset

The TstPatCmp can be enabled to receive either static pattern or pseudo random pattern from

a remote generator. The Source can be a DSP or the Ser2TSIP block. The TSIP link is selectable

between 0 and 59. The TSIP receive timeslot is selectable between 0 and 511. The

TstPatCmpBlk includes a PRBS pattern comparator (eleven stage LFSR with taps at the 9th and

11th stage). The pattern comparator is able to synchronize itself to the receive bit stream.

After synchronization 125 μs-frames and errors are counted. A time of 125us delay has to be

taken into account, til the comparator has stopped after resetting TstPatCmpRxPatEn bit in

TstPatCmpCtrlReg.

8.4.2.3.1 Test Pattern Comparator Link and Timeslot Register

Address: 0x60, TstPatCmpLnkTsReg

Width: 16 bit

This registers selects timeslot TSIP-link for the test pattern reception.

8.4.2.3.2 Test Pattern Comparator Receive Data Register

Address: 0x62, TstPatRcvDatReg

Width: 8 bit

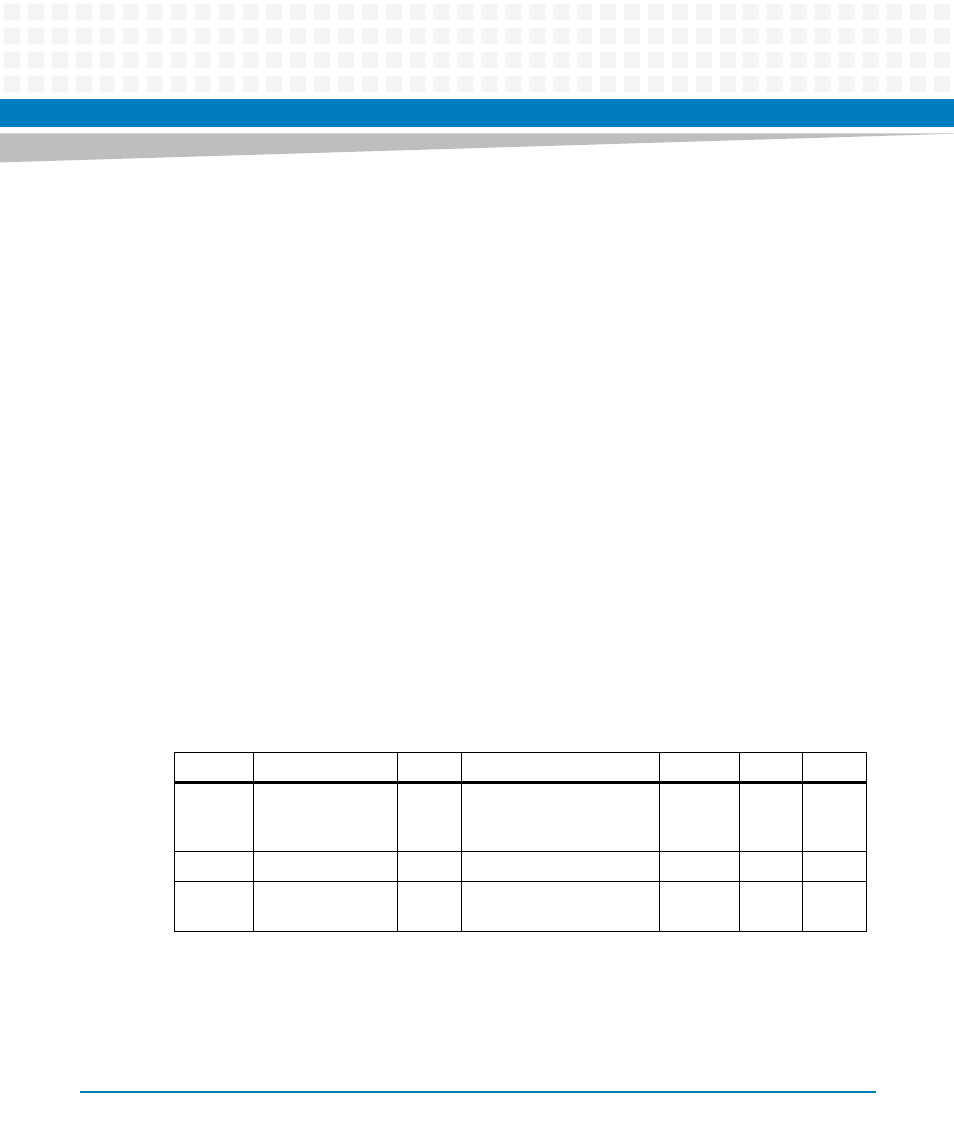

Table 8-179 Test Pattern Comparator Link and Timeslot Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

15...10

TstPatCmpLinkNo

RW

Selects the transmit Link

0..59, (60..63 will be same

as 0)

0x0

X

X

9

-

-

reserved

undef

-

-

8...0

TstPatCmpTsNo

RW

Selects the receive

timeslot (0..511)

0x0

X

X