Table 8-124, Glue logic fpga code spi data register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 325

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

325

5:1

Reserved

0

r

6

SPI Busy Bit:

0: Ready for next read or write access

1: Busy. The SPI clock is still toggling.

0

SPP: r

7

Enable FPGA Code Program Interface

0: Program Interface disabled. Bit 0 is always 1. Write to FPGA Code

SPI Data Register is ignored and read deliver 0.

1: Program Interface enabled. Chip Select is controlled by Bit 0 and

read and write accesses to FPGA Code SPI Data Register are

accepted.

0

SPP: r/w

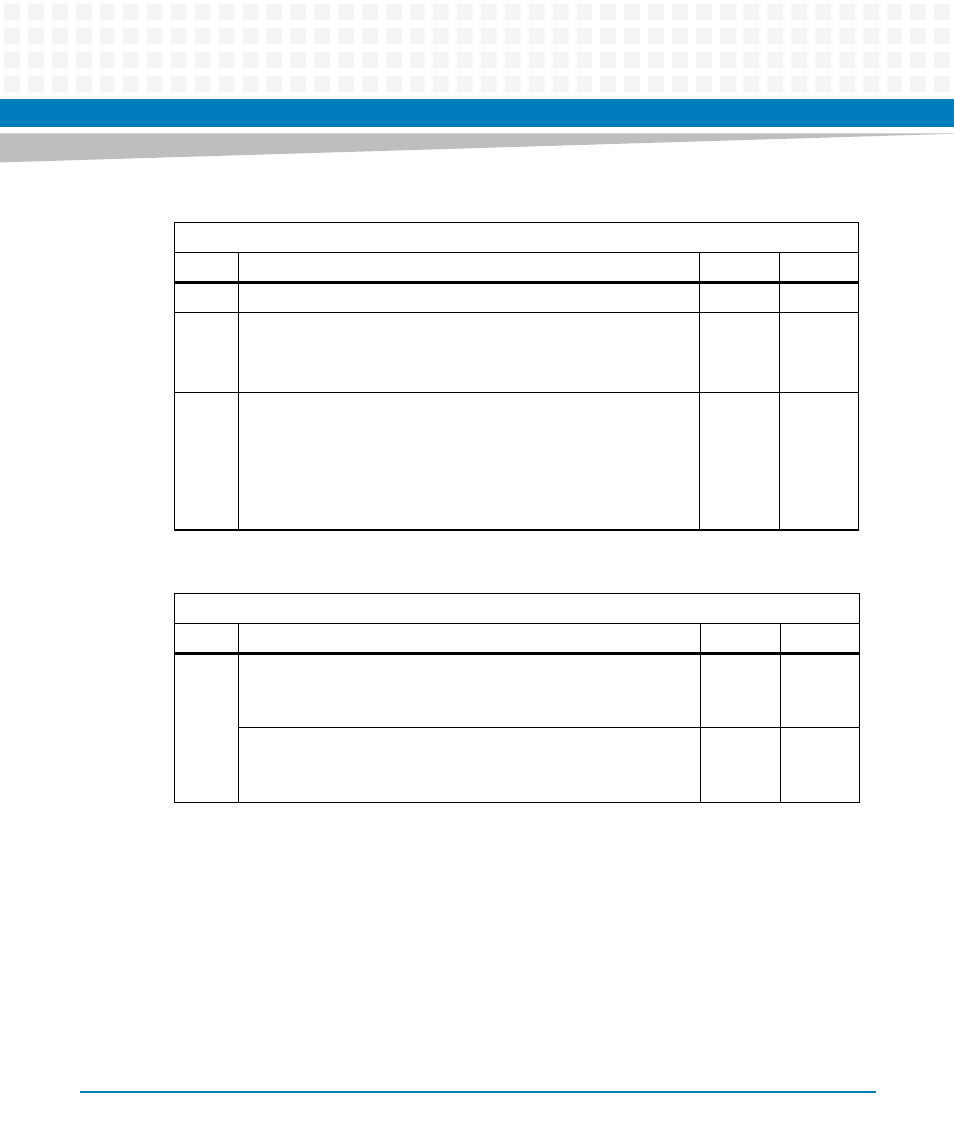

Table 8-124 Glue Logic FPGA Code SPI Data Register

Address: 0x73

Bit Description

Default

Access

7:0

FPGA Code SPI Write Data Register.

A write triggers 8 SPI clocks and shifts the data out to MOSI. The

Data on MISO is shifted in.

-

SPP: w

FPGA Code SPI Read Data Register.

Contains the data shifted in by the last write access to FPGA Code

SPI Data Register

0

SPP: r

Table 8-123 Glue Logic FPGA Code SPI Control Register (continued)

Address: 0x72

Bit Description

Default

Access