Table 8-37, Super io device revision register, Table 8-38 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 271: Super io lpc control register, Table 8-39, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

271

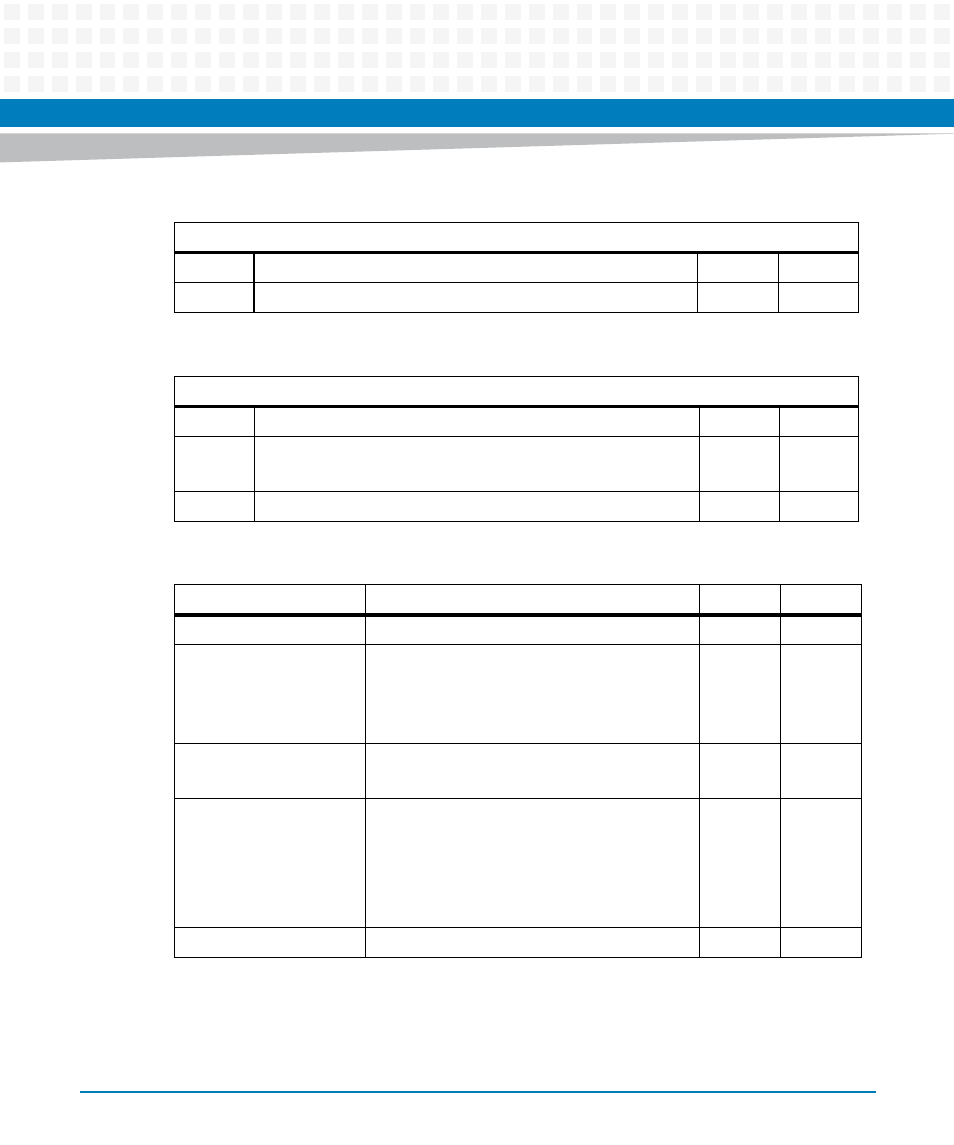

Table 8-37 Super IO Device Revision Register

Index Address: 0x21

Bit

Description

Default

Access

7:0

Device Revision

0x01

GPP: r

Table 8-38 Super IO LPC Control Register

Index Address: 0x28

Bit

Description

Default

Access

0

LPC Bus Wait States:

1: Long wait states (sync 6)

1

GPP: r

7:1

Reserved

0

GPP: r

Table 8-39 Global Super IO SERIRQ and Pre-divide Control Register

Index Address: 0x29

Bit

Description

Default

Access

0

SERIRQ enable:

0: disabled. Serial interrupts disabled.

1: enabled. Logical devices participate in

interrupt generations.

0

GPP: r/w

1

SERIRQ Mode:

1: Continuous Mode

1

GPP: r

3:2

UART Clock pre-divide for COM1 and COM2

00: divide by 1

01: divide by 8

10: divide by 26 (CLK_UART is 48 MHz)

11: reserved

0

GPP: r/w

7:4

Reserved

0

r