Table 8-180, Test pattern comparator receive data register, Table 8-181 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 390: Test pattern comparator data register, Table 8-182, Test pattern comparator control register, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

390

This registers holds the received pattern in the case of static pattern reception. Not used in the

case of pseudo random pattern reception.

8.4.2.3.3 Test Pattern Comparator Data Register

Address: 0x63, TstPatCmpDatReg

Width: 8 bit

This registers holds the reference pattern in the case of static pattern reception. Not used in the

case of pseudo random pattern reception.

8.4.2.3.4 Test Pattern Comparator Control Register

Address: 0x64, TstPatCmpCtrlReg

Width: 8 bit

This registers enables either static or pseudo random pattern reception.

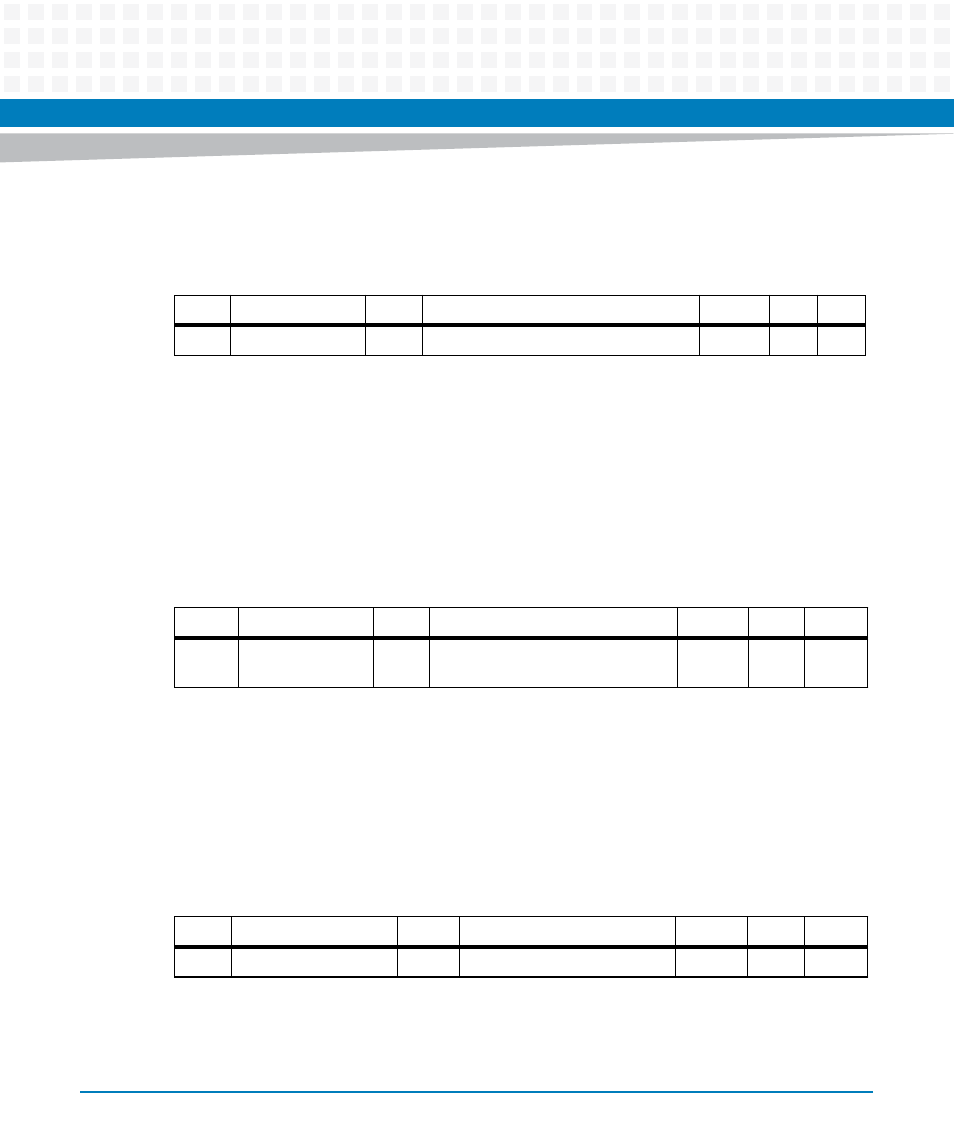

Table 8-180 Test Pattern Comparator Receive Data Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...0

StatRcvdPatData

R

currently received pattern

0x0

X

X

Table 8-181 Test Pattern Comparator Data Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...0

RcvCmpPatData

RW

Compare pattern for the static

pattern reception.

0x0

X

X

Table 8-182 Test Pattern Comparator Control Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...4

-

-

reserved

undef

-

-