Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 335

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

335

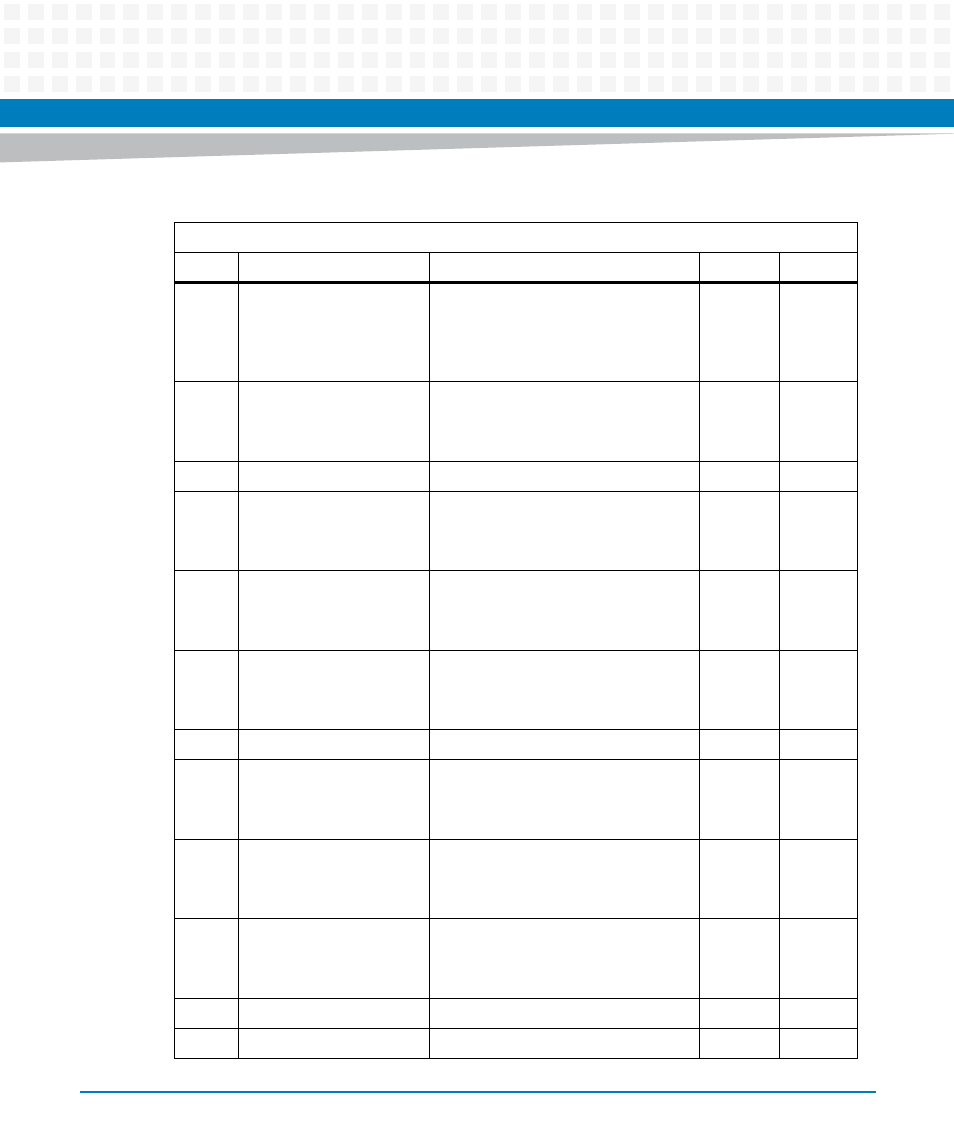

1

DMC_HOUT_DSP_

DMC Base signals host interrupt

enable.

0: Disabled

1:Enabled

0

SPP: r/w

2

DMC_PWRGD

DMC Base power good fail enable.

0: Disabled

1:Enabled

0

SPP: r/w

3

-

Reserved

0

r

4

DMC1_CONF_CRC_ERR

DMC 1 signals a critical error enable.

0: Disabled

1:Enabled

0

SPP: r/w

5

DMC1_HOUT_DSP_

DMC 1 signals host interrupt enable.

0: Disabled

1:Enabled

0

SPP: r/w

6

DMC1_PWRGD

DMC 1 power good fail enable.

0: Disabled

1:Enabled

0

SPP: r/w

7

-

Reserved

0

r

8

DMC2_CONF_CRC_ERR

DMC 2 signals a critical error enable.

0: Disabled

1:Enabled

0

SPP: r/w

9

DMC2_HOUT_DSP_

DMC 2 signals host interrupt enable.

0: Disabled

1:Enabled

0

SPP: r/w

10

DMC2_PWRGD

DMC 2 power good fail enable.

0: Disabled

1:Enabled

0

SPP: r/w

11

-

Reserved

0

r

15:12

-

Reserved for ARMT

0

r

Table 8-141 Cascade Interrupt Enable Register (continued)

Address: 0x94 - 0x95

Bit Interrupt

Signal

Description

Default

Access