Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 377

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

377

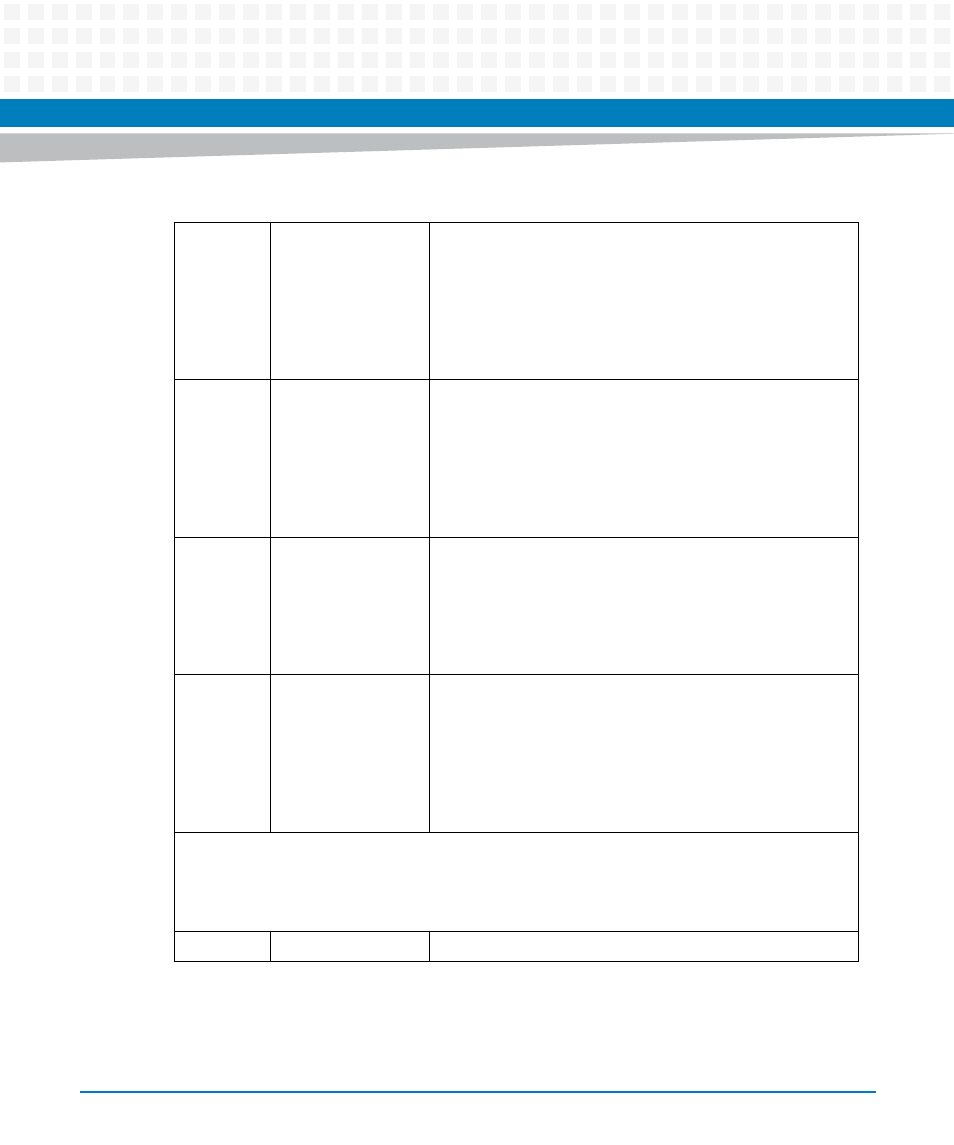

0x88

TstFrameCntReg

Test Frame Count Register (32bit ) [Hw: asyn , WAck2 , RAck2]

This register indicates the number of 125 μs frames since

starting the frame sync counting by

Des2TsipErrCntCtrlReg:FrameCntStart bit. During 125 μs one

SerDes frame is received. Each frame contains a static test

pattern and a CRC checksum

0x8C

SupplTstPatErrCntRe

g

Supplemental Test Pattern Error Count Register (32bit ) [Hw:

asyn, WAck2, RAck2]

This register indicates the number of the test pattern errors

since starting the static pattern reception by the

pErrCntCtrlReg:SupplTstPatErrCntStart bit. The counter sticks

at 0xFFFF_FFFF.

0x90

CrcErrCntReg

CRC Error Count Register (32bit ) [Hw: asyn, WAck2, RAck2]

This register indicates the number of the CRC errors since

enabling the CRC error counting by the

ErrCntCtrlReg:CrcErrCntStart bit. The error counter sticks at

0xFFFFFF.

0x94

DispErrCntReg

Disparity Error Count Register (32bit) [Hw: asyn, WAck2,

RAck2]

This register indicates the number of the Disparity errors since

enabling the Disparity error counting by the

ErrCntCtrlReg:DispErrCntStart bit. The error counter sticks at

0xFFFFFF.

DSP Reset and NMI Control Block (DspResNmiCtrlBlk) [Hw: Cy0]

This block controls the reset and NMI pins to ten TI Tomahawk DSPs (TMS320TCI6486)

Access via SPI- bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block:

98...9F

Address

Acronym

Description

Table 8-174 Logic DSP FPGA Register Overview (continued)