Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 379

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

379

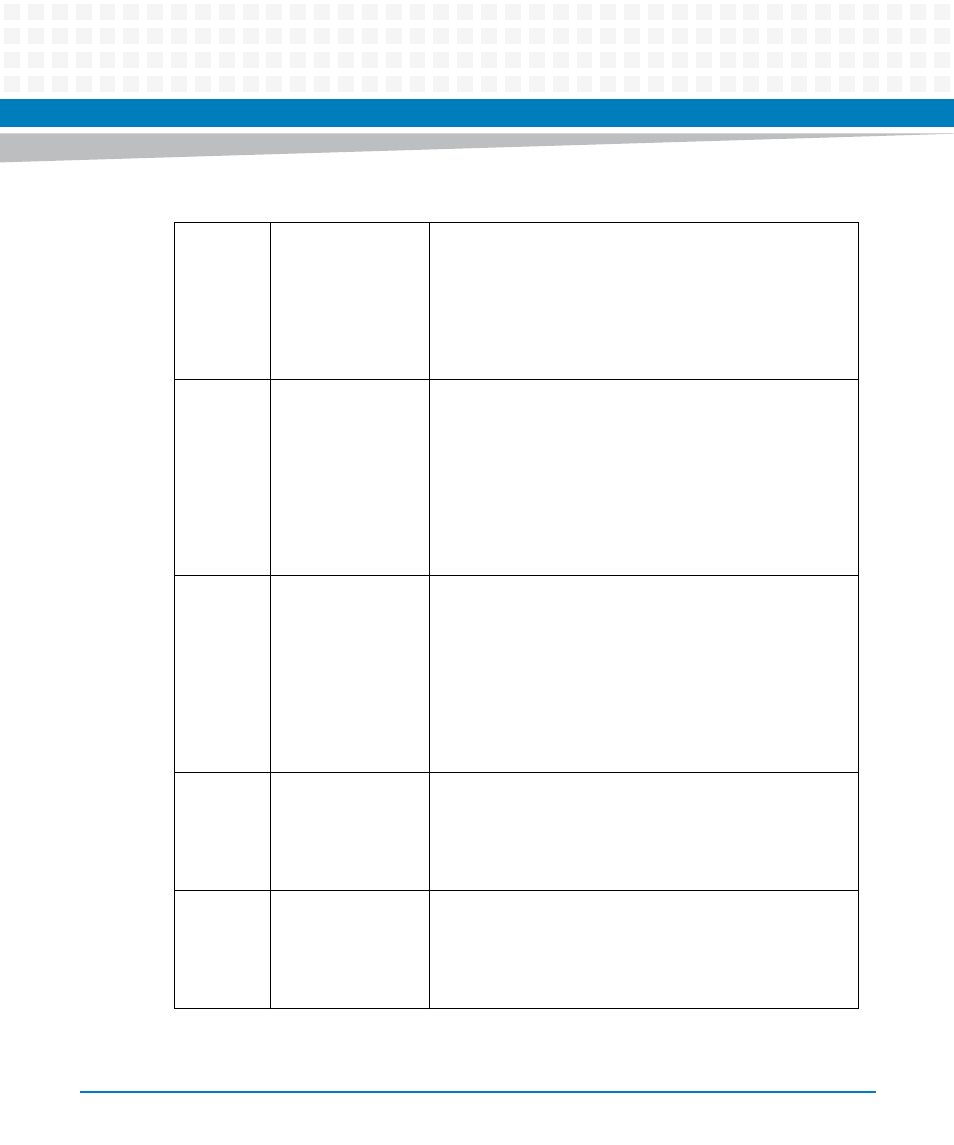

0xA6

DspHevStaReg

DSP Host Event Interrupt Status Register (16bit) [Hw: syn ,

WAck1, RAck1]

This register monitors the Host Event interrupt status of 10

DSPs. If a Host Event Interrupt occurs, the respective bit is set.

It can be reset by writing the respective bit in

DspHevStaResReg.

0xA8

DspWdgStaResReg

DSP Watchdog Interrupt Status Reset Register (16bit) [Hw:

syn, WAck1, RAck1]

The bits of this register reset the respective bits in

DspWdgStaReg. Writing a 1 to a bit in DspWdgStaResReg

resets the corresponding bit in DspWdgStaReg. The interrupt

bit in DspWdgStaReg is kept reset until writing a 0 to the

corresponding bit in DspWdgStaResReg reenables its monitor

function.again.

0xAA

DspHevStaResReg

DSP Host Event Interrupt Status Reset Register (16bit) [Hw:

syn, WAck1, RAck1]

The bits of this register reset the respective bits in

DspHevStaReg. Writing a 1 to a bit in DspHevStaResReg

resets the corresponding bit in DspHevStaReg. The interrupt

bit in DspHevStaReg is kept reset until writing a 0 to the

corresponding bit in DspHevStaResReg reenables its monitor

function.again.

0xAC

DspWdgStaMaskRe

g

DSP Watchdog Interrupt Status Mask Register (16bit) [Hw:

syn, WAck1, RAck1]

The bits of this register mask the bits of the DspWdgStaReg

for the generation of the Host Event Interrupt (HOUT).

0xAE

DspHevStaMaskReg

DSP Host Event Interrupt Status Mask Register (16bit ) [Hw:

syn, WAck1, RAck1]

The bits of this register mask the bits of the DspHevStaReg for

the generation of the Host Event Interrupt (HOUT).

Table 8-174 Logic DSP FPGA Register Overview (continued)